Ramanathan, Parameswaran ProQuest Dissertations and Theses; 1989; ProQuest

# INFORMATION TO USERS

The most advanced technology has been used to photograph and reproduce this manuscript from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book. These are also available as one exposure on a standard 35mm slide or as a 17" x 23" black and white photographic print for an additional charge.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

University Microfilms International A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

Order Number 9013992

Synchronization and distributed agreement in real time systems

Ramanathan, Parameswaran, Ph.D.

The University of Michigan, 1989

# SYNCHRONIZATION AND DISTRIBUTED AGREEMENT IN REAL-TIME SYSTEMS

by

#### Parameswaran Ramanathan

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 1989

# Doctoral Committee:

Professor Kang G. Shin, Chairman Assistant Professor Chaitanya K. Baru Associate Professor John R. Birge Assistant Professor Richard B. Brown Professor John P. Hayes

# RULES REGARDING THE USE OF MICROFILMED DISSERTATIONS

Microfilmed or bound copies of doctoral dissertations submitted to The University of Michigan and made available through University Microfilms International or The University of Michigan are open for inspection, but they are to be used only with due regard for the rights of the author. Extensive copying of the dissertation or publication of material in excess of standard copyright limits, whether or not the dissertation has been copyrighted, must have been approved by the author as well as by the Dean of the Graduate School. Proper credit must be given to the author if any material from the dissertation is used in subsequent written or published work.

© <u>Parameswaran Ramanathan</u> 1989 All Rights Reserved To my parents

# **ACKNOWLEDGEMENTS**

It is an impossible undertaking to thank all those who have contributed to the success of this dissertation. I would, however, like to take this opportunity to thank a few who have influenced me the most.

First and foremost, I would like to thank my advisor, Professor Kang G. Shin. Professor Shin's constant support helped me wade through the frustrations and the triumphs of a graduate program. Through his guidance I have gained invaluable expertise on approaching, analyzing and solving problems that are presented to me. I would also like to express my appreciation to other members of the doctoral committee, Professors Chaitanya Baru, John Birge, Richard Brown and John Hayes for their constructive criticisms on this dissertation. Thanks also goes to the National Aeronautics and Space Administration, Office of Naval Research, and Horace H. Rackham School of Graduate Studies for providing the funds necessary for this research.

Heartfelt thanks to James Dolter and Dilip Kandlur for all the daily discussions that helped me formulate the ideas in this dissertation. This work could not have been accomplished without their constant encouragement. I would also like to acknowledge Dilip Kandlur for his assistance in formulating some of the ideas in software synchronization that are presented in Chapter 2. Thanks also to Alan Olson and Daniel Kiskis for the helpful comments on the early versions of this manuscript.

Finally, I would like to thank my parents for their moral support during this effort. Their contribution to this dissertation cannot be measured.

# TABLE OF CONTENTS

| DEDIC  | ATION                                   | ii  |

|--------|-----------------------------------------|-----|

| ACKNO  | OWLEDGEMENTS                            | iii |

| LIST O | OF TABLES                               | vi  |

| LIST C | OF FIGURES                              | vii |

| CHAPI  | TER                                     |     |

| 1.     | INTRODUCTION                            | 1   |

|        | 1.1 Motivation                          | 1   |

|        | 1.2 Prior Work                          | 3   |

|        | 1.3 Research Objectives                 | 5   |

|        | 1.4 Outline of the Dissertation         | 7   |

| 2.     | SYSTEM LEVEL SYNCHRONIZATION            | 9   |

|        | 2.1 Introduction                        | 9   |

|        | 2.2 Related Research                    | 10  |

|        | 2.3 Terminology                         | 13  |

|        | 2.4 A Hardware Synchronization Scheme   | 14  |

|        | 2.5 A Software Synchronization Scheme   | 32  |

|        | 2.6 Discussion                          | 52  |

| 3.     | CLOCK DISTRIBUTION WITHIN VLSI CIRCUITS | 55  |

|        | 3.1 Introduction                        | 55  |

|        | 3.2 Problem Formulation                 | 57  |

|        | 3.3 Selection of the Entry Point        | 64  |

|        | 3.4 Optimization Problem                | 69  |

|        | 3.5 Implementation                                         | 72  |

|--------|------------------------------------------------------------|-----|

|        | 3.6 Discussion                                             | 76  |

| 4.     | CHECKPOINTING AND ROLLBACK RECOVERY USING COMMON TIME BASE | 77  |

|        | 4.1 Introduction                                           | 77  |

| -      | 4.2 Related Research                                       | 78  |

|        | 4.3 Checkpointing and Rollback Recovery Scheme             | 80  |

|        | 4.4 Discussion                                             | 102 |

| 5.     | DIAGNOSIS OF BYZANTINE FAULTS                              | 103 |

|        | 5.1 Introduction                                           | 103 |

|        | 5.2 Related Research                                       | 105 |

|        | 5.3 Issues in diagnosis of Byzantine faults                | 107 |

|        | 5.4 Diagnosis Scheme                                       | 111 |

|        | 5.5 Discussion                                             | 122 |

| 6.     | DISCUSSION AND FUTURE WORK                                 | 124 |

| ini ic | ACD A DILIV                                                | 107 |

# LIST OF TABLES

# <u>Table</u>

| 1.1 | Comparison of a few ultra-reliable systems                                  | 4   |

|-----|-----------------------------------------------------------------------------|-----|

| 2.1 | Proposed interconnection scheme for an 8 clock system                       | 19  |

| 2.2 | Variations in number of interconnections with size of the system            | 28  |

| 2.3 | Variations in number of interconnections with fault tolerance specification | 30  |

| 4.1 | Expected overheads in the proposed checkpointing scheme                     | 102 |

# LIST OF FIGURES

| Figu | <u>re</u>                                                            |    |

|------|----------------------------------------------------------------------|----|

| 2.1  | Block diagram of the hardware synchronization scheme                 | 14 |

| 2.2  | Delay Elimination Block                                              | 16 |

| 2.3  | Illustration of case $ OF_i  <  IN_k $ for Lemma 2.2                 | 24 |

| 2.4  | Illustration of the case $ OF_i  \geq  IN_k $ for Theorem 2.2        | 26 |

| 2.5  | % Reduction over a fully connected network versus size of the system | 29 |

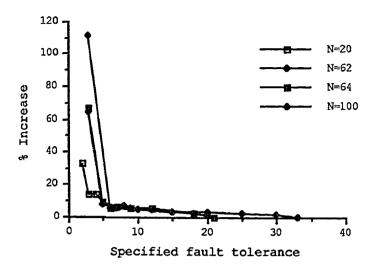

| 2.6  | % Increase versus specified fault tolerance                          | 31 |

| 2.7  | CLOCK_SEND task at node p                                            | 37 |

| 2.8  | CLOCK_RELAY task                                                     | 37 |

| 2.9  | CLOCK_RECEIVE task                                                   | 38 |

| 2.10 | Clock_Correction task                                                | 39 |

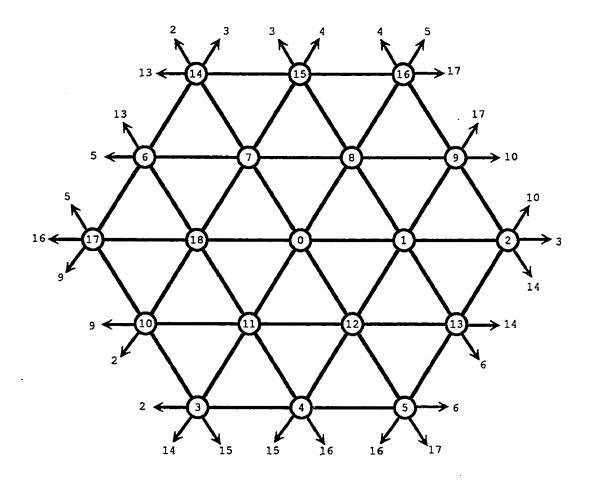

| 2.11 | A C-wrapped hexagonal mesh of dimension 3                            | 50 |

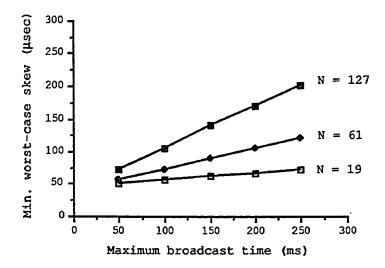

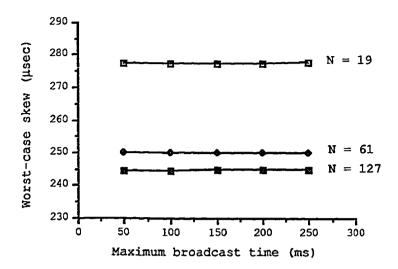

| 2.12 | Min. worst-case skew versus Max. broadcast time for a hexagonal mesh | 51 |

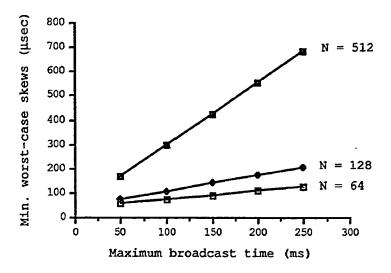

| 2.13 | Min. worst-case skew versus Max. broadcast time for a hypercube      | 52 |

| 2.14 | Worst-case skew versus Max. broadcast time for a hexagonal mesh      | 53 |

| 2.15 | Worst-case skew versus Max. broadcast time for a hypercube           | 53 |

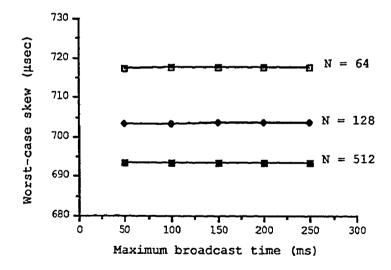

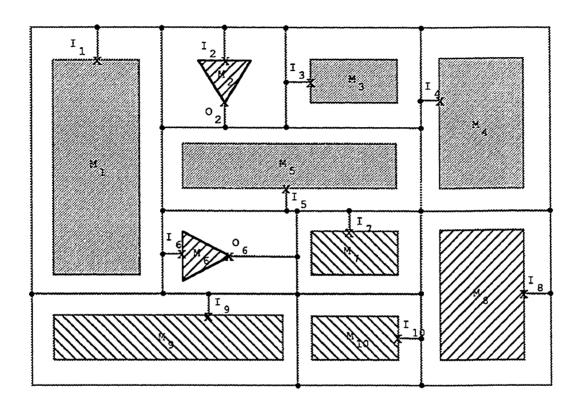

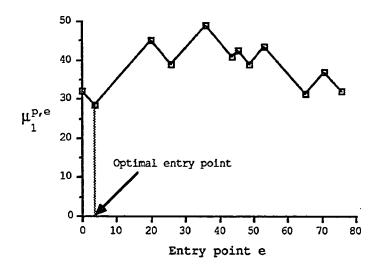

| 3.1  | Floorplan of sub-modules in $M$                                      | 62 |

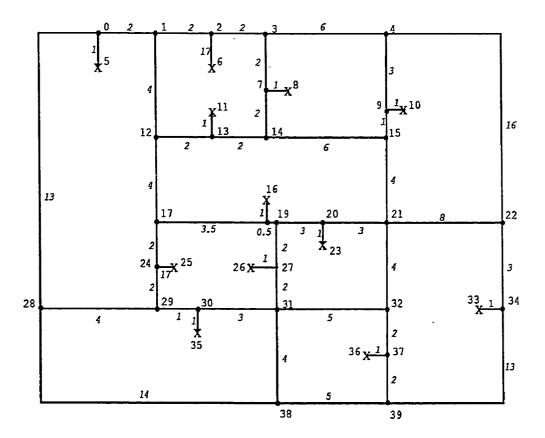

| 3.2  | Placement graph.                                                     | 63 |

| 3.3  | Algorithm Entry                                                      | 68 |

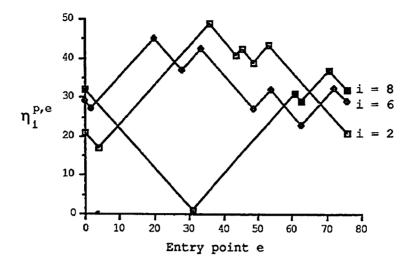

| 3.4  | Variation in $\eta_i^{P,e}$ for the floorplan in Figure 3.1          | 69 |

| 35   | Variation in $u^{P,e}$ for the floorplan in Figure 3.1               | 70 |

| 3.6 | Algorithm Route                                                  | 72  |

|-----|------------------------------------------------------------------|-----|

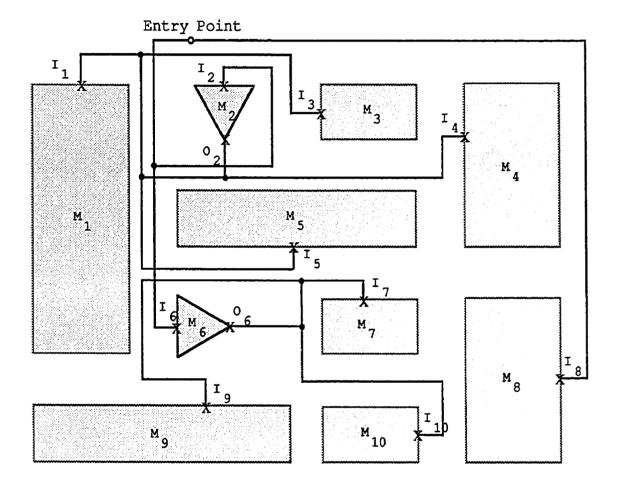

| 3.7 | Optimal clock layout for floorplan in Figure 3.1                 | 74  |

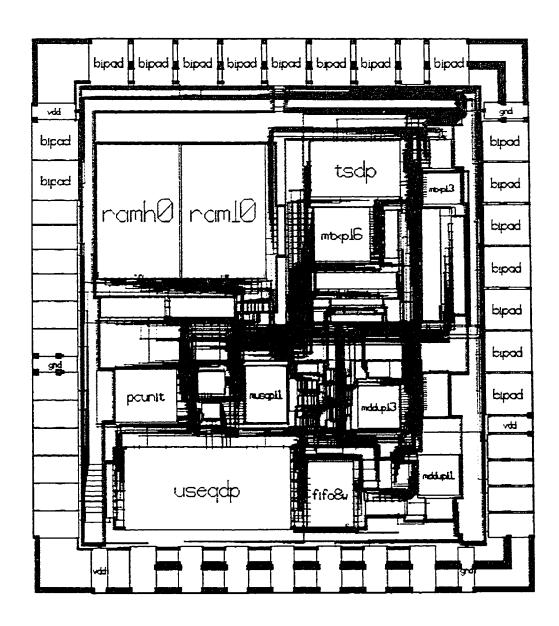

| 3.8 | Floorplan of the custom VLSI chip                                | 76  |

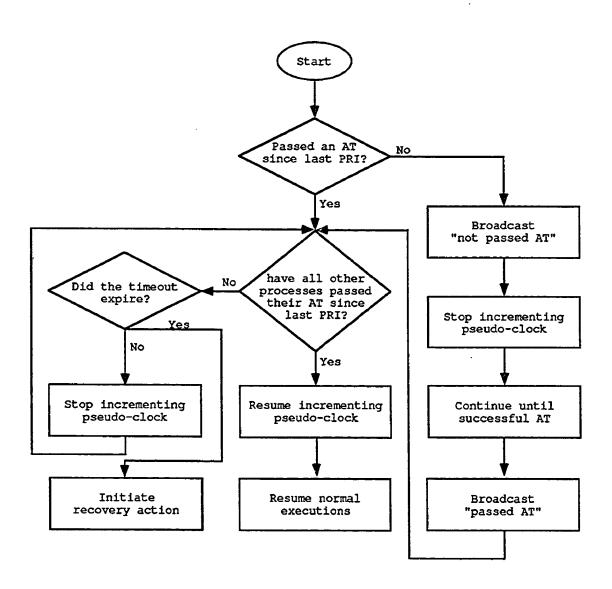

| 4.1 | Flowchart of the interrupt handler for PRI                       | 87  |

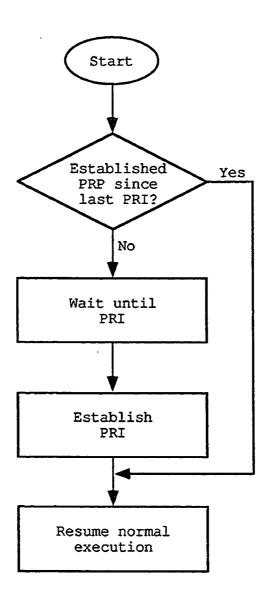

| 4.2 | Interrupt handler for PRI                                        | 88  |

| 4.3 | Flowchart of the interrupt handler for ATI                       | 90  |

| 4.4 | Interrupt handler for ATI                                        | 91  |

| 4.5 | Interrupt handler of EI                                          | 91  |

| 4.6 | Maintenance procedure for pseudo-clock                           | 91  |

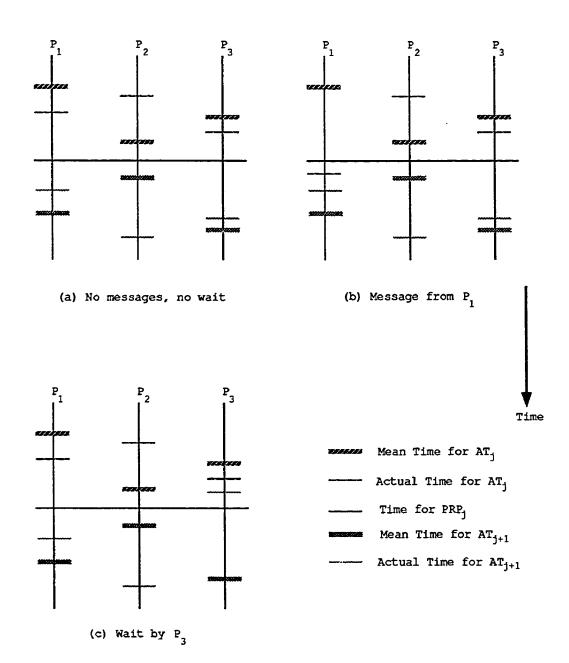

| 4.7 | Illustration of checkpointing algorithm                          | 93  |

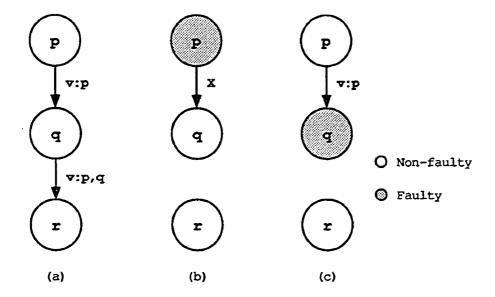

| 5.1 | An example of a non-faulty node accusing another non-faulty node | 109 |

| 52  | Unmodified and modified distributed agreement algorithms         | 116 |

#### **CHAPTER 1**

# INTRODUCTION

# 1.1 Motivation

The potential for applying digital computers to real-time control is enormous. It is just beginning to be recognized that computers have a vital role in controlling many critical processes. This is especially true in applications such as the control of aircraft, spacecraft, life-support systems, nuclear power plants, automobile engines, and process control plants, where the time available for responding to the environment is always becoming shorter.

The control computers in these applications are required to be fast and highly reliable. These requirements are stringent because a single failure in the control system can be catastrophic. Fault tolerance is therefore a major issue in the design of these control computers. The exact nature of fault tolerance that needs to be incorporated depends on the application. Some applications require very high reliability for a short period of time while others require moderate reliability over a long period. For example, in a commercial transport aircraft the duration of a flight is around 10 hours and the allowable probability of failure per mission is specified as  $10^{-9}$ . In contrast, in a manned space flight, the duration of a mission is relatively long, around 10 days, while the allowable probability of failure per mission is higher by about two orders of magnitude. Besides, in a commercial transport aircraft there is no facility for repair during a mission as compared to some facility for repair in a manned space flight. Several such factors along with the potential loss in case of a failure determine the fault tolerance capabilities that needs to be incorporated in a system.

Given the fault tolerance requirements, it is still very difficult to show that the designed system will actually meet those requirements. Since the cost incurred upon failure is extremely high, the control computers for these applications are often designed under the worst-case assumption that the faulty components can do whatever they like. This includes altering, blocking, re-routing or in the worst case, sending conflicting information to different parts of the system. A component that exhibits this type of behavior is commonly referred to as being *malicious*, and the fault model is referred to as the *Byzantine fault model*.

As one can easily imagine, Byzantine faults pose serious problems in all three major activities of a real-time control system, namely, acquisition of data from the input sensors, the processing of acquired data and writing of output data to the actuators. For example, it is often necessary for the components in a real-time system to reach a consensus on the value read from an input sensor. In the absence of Byzantine faults, this consensus can be easily achieved by using some form of redundancy. For instance, multiple components can independently read and exchange the value of a sensor with other components, and then use an appropriate fault-tolerant "averaging" function to arrive at a mutually agreeable value. This problem however gets complicated when malicious components report conflicting values to different parts of the system, thus causing them to arrive at contradictory results.

Several techniques have been put forth for ensuring consensus among the non-faulty components in the presence of Byzantine faults [7, 9, 11, 12, 13, 37, 66]. Most of these solutions require an excessive amount of time to execute and are, therefore, unsuitable for real-time applications. The objectives of this dissertation are to address ways of eliminating/reducing the time overhead imposed by these solutions and simplifying the design of computer systems that are resilient to Byzantine faults. The emphasis is on developing fault-tolerant methods for synchronizing system components and ensuring distributed agreement among cooperating processes.

This work is significant because almost all time and mission critical applications use some form of distributed processing to meet their reliability and performance requirements. In these systems, the coordination among concurrent processes is by exchanging information. The information may in general be input data, output data, clock values, system status, or any other data relevant to the system. Agreement by definition is a consensus among the participating components on any such information and hence, important in all distributed systems. Likewise,

synchronization is important in all distributed systems because: (i) it is essential for ensuring distributed agreement, (ii) it can simplify fault-tolerant algorithms for several design problems including inter-process communication, checkpointing and rollback recovery, resource allocation, and transaction processing and (iii) it can be used to implement features like deadlines and timeout that are essential for correct operation of any distributed real-time system.

#### 1.2 Prior Work

Techniques for designing computer systems that can tolerate Byzantine faults are well-understood. The following four conditions have been shown to be necessary for any algorithm that is resilient to m Byzantine faults. This includes algorithms for synchronization as well as distributed agreement.

- 1. There must be at least 3m + 1 participants in the algorithm [44].

- 2. Each participant must be connected to at least 2m + 1 other participants through disjoint communication paths [7].

- 3. The protocol must consist of a minimum of m + 1 rounds of communication among the participants [12].

- 4. The participants must be synchronized to within known skews of each other [8, 16].

Based on these theoretical developments several ultra-reliable computer systems have been built over the past decade. This includes systems such as the Fault-Tolerant MultiProcessor (FTMP) [25, 62], Software Implemented Fault Tolerance (SIFT) [20], Fault Tolerant Processor (FTP) [61], Multicomputer Architecture for Fault Tolerance (MAFT) [30], and Advanced Information Processing System (AIPS) [26]. A comparison between these systems is shown in Table 1.1.

As indicated in the table, SIFT is a six processor system with direct connection between all pairs of processors. It uses a software synchronization scheme to maintain the clocks to within known skews of each other. In comparison, FTMP is a ten processor system organized in the form of three triads and a spare. The communication between the triads is through a 5-way redundant

| System # of proc. |                               | Topology                   | Sync. algorithm | Multiprocessing |  |

|-------------------|-------------------------------|----------------------------|-----------------|-----------------|--|

| SIFT              | 6                             | Fully connected            | Software        | Yes             |  |

| FTMP              | 10                            | Broadcast bus              | Hardware        | Yes             |  |

| FTP               | ≤4                            | See note 1                 | Hardware        | No              |  |

| MAFT 8            |                               | Broadcast bus Software Yes |                 | Yes             |  |

| AIPS              | AIPS See note 2 Broadcast bus |                            | See note 3      | Yes             |  |

Note 1: Special data exchange network.

Note 2: Limited by contention for the broadcast bus.

Note 3: Still being designed.

Table 1.1: Comparison of a few ultra-reliable systems

broadcast bus with three active and two spares. Unlike SIFT, it uses a hardware synchronization scheme to maintain the clocks close to one another.

In direct contrast to FTMP and SIFT, FTP is a much simpler design that can execute only one instruction stream at any given time (the redundant processors are solely for fault tolerance). However, like FTMP it uses a hardware scheme to tightly synchronize its clocks. On the other hand, MAFT is a distributed system comprised of eight semi-autonomous nodes connected through a broadcast bus network. It uses a software scheme similar to that of SIFT to maintain a loose synchronization between its clocks. AIPS is a distributed system comprised of fault tolerant multiprocessors interconnected through a redundant virtual bus. The number of fault tolerant multiprocessors in AIPS is limited by the contention for the virtual bus.

At the outset, these systems may seem to be widely varied from each other. However, there are several common features among them that are typical to the existing algorithms for tolerating Byzantine faults. First, all of the above systems except AIPS are small and tightly coupled multiprocessors. Second, they can tolerate a maximum of one Byzantine fault at any given time. Third, the schemes used in these systems cannot often be extended to a multiple fault scenario,

e.g, the hardware synchronization algorithm used in FTMP and FTP. Finally, even though all the above systems have extensive capabilities for reconfiguration, there exists no fault detection algorithm that is guaranteed to always identify the malicious components.

In contrast, the goal of this dissertation is to consider systems that are large and loosely-coupled. The systems are also assumed to be partially connected through a point-to-point inter-connection network as opposed to a broadcast bus or a fully connected network. The reliability requirements of the systems are also assumed to be such that it may be necessary to tolerate more than one Byzantine fault. This work is significant because large partially connected distributed systems are well-suited for meeting the stringent performance and reliability requirements of a critical real-time application.

# 1.3 Research Objectives

The objectives of this dissertation are three-fold:

- develop algorithms for establishing a global time base in the system,

- illustrate the use of global time base to simplify other fault-tolerant algorithms, and

- reduce/eliminate the overheads for synchronization and distributed agreement through diagnosis of Byzantine faults.

The algorithm for establishing a global time base can be considered at two different levels: system level and node level. System level synchronization deals with establishing a time base among the nodes of a distributed system. This problem gets complicated when some of these nodes behave maliciously by providing conflicting clock values to different parts of the system. Additional problems arise in large distributed systems because the existing algorithms are not easily scalable. In contrast, node level synchronization deals with establishing a global time base among the components in a node by properly distributing a clock signal to all the components.

There are both software and hardware solutions for system level synchronization. The software solutions require nodes to exchange and adjust their clock values periodically. Since the clock values are exchanged via message passing, the time overhead imposed by the software solutions can be substantial, especially if a tight synchronization is desired. The hardware solutions, on

the other hand, use special hardware at each node to achieve a very tight synchronization with minimal overhead. However, the prohibitive cost of the additional hardware limits their usefulness to small distributed systems. Since the choice between the two solutions for a system depends on the application, both these approaches are considered in this dissertation. The emphasis is on reducing the cost of hardware solutions and the worst-case skews of software solutions to make both these alternatives viable even in large distributed systems.

In node level synchronization, the goal is to control the clock skew between the modules in a VLSI circuit to an acceptable small fraction of the clock period. Within a VLSI circuit the clock skews are mainly due to the difference in length of clock lines and due to the difference in the number of clock buffers inserted in the clock lines. The existing schemes for clock distribution are either applicable only in the case of a symmetric placement of the modules such as systolic arrays or they are too detailed and sensitive to the technology and the fabrication process. The emphasis here is on developing a general scheme that is applicable in non-symmetric VLSI circuits. The objective is to determine a layout of clock lines given the floorplan that minimizes the clock skew subject to minimum longest delay.

The use of a global time base to simplify fault-tolerant algorithms is illustrated by considering the checkpointing and rollback recovery schemes. These schemes are mainly used to recover from software errors when cooperating processes are executing concurrently in a distributed system. It is shown that the number of messages as well as the waiting time for checkpointing and rollback recovery can be reduced substantially by using the global time base. The only additional cost in this scheme as compared to other known schemes is the cost of establishing the time base.

The cost of synchronization, and hence the cost of establishing a global time base, depends on the maximum number of Byzantine faults to be tolerated. Given the reliability requirements of a system, the number of faults that needs to be tolerated can be reduced by preventing the accumulation of Byzantine faults by diagnosing them as soon as they occur. This work can be used to reduce the overheads imposed by synchronization algorithms and various other algorithms that are resilient to Byzantine faults. It is therefore presented in a more general context of distributed agreement.

#### 1.4 Outline of the Dissertation

This dissertation is organized as follows. Chapter 2 deals with the problems related to synchronizing large distributed systems. It discusses solutions to two major problems in the existing hardware synchronization algorithms, namely, the assumption that there is a fully connected network of clocks and the assumption that the transmission delay from one clock to another is negligible. These two assumptions are difficult to satisfy in a large distributed system. The scheme discussed requires only 20–30 percent of the total number of interconnections required by a fully connected network for almost no loss in synchronization capabilities. This is achieved by grouping the clocks into clusters and treating the clusters as clock units as far as the system is concerned. The effects of the transmission delay are reduced by a technique traditionally used in the communication area called the returnable timing system.

Chapter 2 also discusses a hardware-assisted software solution for synchronizing large partially connected distributed systems. As compared to the hardware solution, this scheme requires minimal additional hardware at each node and does not require a separate network of clocks. It is suitable for synchronizing specific interconnection topologies like a hypercube or a C-wrapped hexagonal mesh, especially when a very tight synchronization is not essential. The skews achieved are, however, much tighter than that of the existing software schemes.

The problem of synchronizing different modules in a VLSI circuit is addressed in Chapter 3. The hierarchy created by clock buffers is used to distribute the clock signal to the modules. Unlike other related work in this area, both delay and skew are taken into account in determining the layout. The resulting scheme can be easily parallelized.

A checkpointing and rollback recovery algorithm that is based on the existence of a global time base is presented in Chapter 4. The existence of a global time base is coupled with the idea of pseudo-recovery block approach to develop an algorithm that has the advantages of maximum process autonomy, minimal wait for commitment, fewer messages and less memory requirement. A probabilistic model to evaluate these advantages is also developed.

A novel approach for reducing the overheads imposed by synchronization and distributed agreement algorithms is presented in Chapter 5. The reduction in overhead is achieved through diagnosis of Byzantine faults. The algorithm for diagnosis is such that there is an upper bound

on the number of times a node can exhibit its Byzantine behavior without being identified.

Chapter 6 is a discussion on future research directions based on the results presented in this dissertation.

#### **CHAPTER 2**

# SYSTEM LEVEL SYNCHRONIZATION

# 2.1 Introduction

A global time base is widely recognized as an important requirement in distributed real-time systems. It is essential for problems like distributed agreement and also for implementing features like deadlines and timeout. It can also be used to simplify solutions to several other problems like checkpointing, inter-process communication, resource allocation, and transaction processing.

The global time base can be established by synchronizing all the local clocks in the system. These synchronizing operations would not be much of a problem had all the clocks, including the faulty ones, behaved consistently with one another. However, when some of the faulty clocks can behave in an arbitrary manner, these synchronizing operations present some serious problems. For instance, a faulty clock can make it difficult for the other clocks to synchronize themselves by sending conflicting information during the course of synchronization. Lamport and Melliar-Smith referred to this kind of behavior as a *Byzantine fault* and were the first to develop a solution for synchronizing clocks in the presence of these faults [35, 36]. Since then, this problem has been studied extensively and several software and hardware solutions have been proposed.

The software solutions are flexible and economical but require additional messages to be exchanged solely for synchronization [22, 36, 43, 64]. Due to the dependence on message exchanges, the worst-case skews guaranteed by most of these solutions are greater than the maximum message transit delay between any two nodes in the system. The hardware solutions, on the other hand, use special hardware at each node to achieve a very tight synchronization with

minimal time overhead [29, 33, 57, 67]. However, the cost of additional hardware precludes their use in large distributed systems unless a very tight synchronization is essential. The hardware solutions also require a separate network of clocks that is different from the interconnection network between the nodes of the distributed system [57].

The choice between hardware and software synchronization methods has to be made based on the application and the characteristics of the system. The goal of this dissertation is to make both methods viable alternatives for synchronizing large distributed systems. This goal is realized by addressing the specific drawbacks of these two methods, namely the cost of hardware solutions and the guaranteed worst-case skew of software solutions.

This chapter is organized as follows. A survey of related work in both hardware and software synchronization methods is presented in the following section. The terminology that is common to both these methods is introduced in the third section. The drawbacks in hardware and software synchronization methods are addressed in the fourth and the fifth sections. The sixth section discusses the relative merits of the schemes proposed.

# 2.2 Related Research

The principle of hardware synchronization algorithms is that of a phase-locked loop. Each individual clock is an output of a voltage controlled oscillator. The voltage applied to the oscillator comes from a phase detector whose output is proportional to the phase error between the phase of its clock (i.e., the output of the voltage controlled oscillator it is controlling) and a reference signal generated by using the other clocks in the system. Thus, by adjusting the frequency of each individual clock to the reference signal, the clocks can always be kept in lock-step with respect to one another.

As of today, there have been only two implementations of this approach [19, 62]. Both these implementations use four clocks and can tolerate only one Byzantine fault. An extension of the algorithms in [19, 62] to tolerate more than one of Byzantine fault is non-trivial and is described in [29, 33, 67]. The principle in [29, 33, 67] is the same as in [19, 62], but the selection of the reference signal is more complicated. Each node receives the clocks at other nodes as inputs and orders them as per the time of their arrival. The position of its own clock in this ordered sequence

is used to correct its clock in the subsequent cycles. In [29], the number of clocks that are faster than its own clock is used to derive the control voltage while in [33] the phase difference between a chosen reference signal and its own clock is used as the control voltage. In [67], two reference signals are selected from the ordered sequence and a combination of the phase difference between its clock and the two reference signals is used as the control voltage.

There are several problems associated with synchronizing large distributed systems using the algorithms in [29, 33, 67]. The first problem is that all of the above algorithms require a fully connected network of clocks. Due to the large number of interconnections in a fully connected network, the reliability of synchronization will be determined by the failure rates of these interconnections rather than the failure rate of the clocks. Furthermore, there will be problems of fan-in and fan-out caused by the large number of interconnections. The second problem with the above algorithms is that they are based on the assumption that the transmission delays between the clocks are negligible as compared to desired worst-case skew. In a large system, the physical separation between a pair of clocks can be considerable enough to result in non-negligible transmission delays.

Unlike the hardware solutions, software solutions synchronize logical clocks instead of hardware clocks. Given that the hardware clocks drift at a bounded rate from real time, the software solutions periodically exchange and adjust the logical clocks to maintain them sufficiently close to one another [22, 36, 43, 64]. A software solution can be viewed as a process that runs on each node to maintain a time base for all the activities on the node. This clock process is responsible for synchronizing the local logical clock with the other logical clocks in the system.

In [22, 64], the clock process broadcasts a message to other clock processes to indicate that it is ready for resynchronization. This occurs either when its clock reaches a pre-determined time or when it sufficient number of messages from other processes to be sure that at least one other non-faulty process is ready for a resynchronization. During a resynchronization, a new logical clock is started in such a way that it is guaranteed to be close to the clocks started approximately at the same time at other nodes. In [36, 43], a clock process broadcasts its logical clock at a pre-determined time. It then waits for a fixed amount of time to collect similar messages from other processes. At the end of the waiting period, the clock process averages the arrival times of the messages from other clock processes using a fault-tolerant averaging function. The resulting

average is used to compute the adjustment to the local clock.

Because of the dependence of these software schemes on message passing, the guaranteed worst-case skew between the logical clocks is greater than the maximum message transit delay in the system [22, 36, 43, 64]. This is acceptable in a small fully connected system because the maximum message transit delays in such systems are typically quite small. However, in large distributed systems where the nodes are not fully connected, the clock messages may have to be relayed through several intermediate processes before they reach all other processes. This results in large message transit delays which in turn results in poor worst-case skews.

There are some software schemes in which this problem does not occur [2, 15]. In [15], the clocks are intended for simulating the concept of rounds for distributed agreement algorithms rather than to keep track of elapsed time intervals. Hence, their definition of a clock is different from the definition in the other schemes [22, 36, 43, 64]. The definition of a clock in [15] is not sufficient for real-time systems, since it cannot be used to implement important features like deadlines and timeout. The idea in [2] is to assume that the probability distribution of message transit delays is known and let each clock process make several attempts to read the other clocks. At the end of each attempt, it can calculate the maximum error that might occur if the clock value obtained in that attempt is used for determining the correction. By retrying a sufficient number of times, a clock process can read the other clocks to any given precision with probability as close to one as desired. This scheme is particularly suitable for systems that have a master-slave arrangement in which one clock has been designated or elected as a master and the other clocks act as slaves. This again is not suitable for a real-time system because the algorithms to detect a failure of the master and to elect a new one are fairly complex and time-consuming, especially in the presence of Byzantine faults. There is also a non-zero probability of not being able to synchronize the non-faulty clocks due to the probabilistic nature of the clock reading mechanism.

As a consequence, the usefulness of the existing hardware and software synchronization schemes is limited to small distributed systems. An extension of these schemes to large distributed systems is presented below. First, solutions are proposed to overcome the transmission delay and the interconnection problems in hardware synchronization. Then, a hardware-assisted software synchronization scheme is proposed that achieves skews that are about two to three orders of magnitude tighter than the skews in the existing software schemes. This can be used in

systems that cannot afford the cost of additional hardware required in pure hardware solutions. Prior to describing these solutions some of the notations and the terminology are introduced.

# 2.3 Terminology

**Definition 2.1:** The time that is directly observable in some particular clock is called its *clock time*. This should be contrasted to the term *real time*, which is measured in an assumed Newtonian time frame that is not directly observable.

Definition 2.2: Let c be a mapping from clock time to real time, where c(T) = t means that at clock time T the real time is t. Then, two clocks  $c_1$  and  $c_2$  are said to be  $\delta$ -synchronized at a clock time T if and only if  $|c_1(T) - c_2(T)| \le \delta$ . We adopt the convention of using lowercase letters to denote quantities that represent real time and uppercase letters to denote quantities that represent clock time.

**Definition 2.3:** A clock c is said to be a good clock during the real-time interval  $[t_1, t_2]$  if it is a monotonic, differentiable function on  $[T_1, T_2]$  where  $c(T_i) = t_i$ , i = 1, 2, and for all T in  $[T_1, T_2]$ :

$$\left|\frac{dc(T)}{dT} - 1\right| < \frac{\rho}{2}$$

for some constant  $\rho$ . The constant  $\rho$  represents the drift rate of the good clocks.

**Definition 2.4:** A set of clocks are said to be *well-synchronized* if and only if any two non-faulty clocks in this set are  $\delta$ -synchronized for some specified constant  $\delta$ .

Definition 2.5: A well-synchronized set of clocks has a re-synchronization interval. In hardware (software) synchronization, the  $k^{th}$  re-synchronization interval is the time duration between the  $k^{th}$  and the  $(k+1)^{th}$  tick (adjustment) of the fastest non-faulty clock. Note that the fastest non-faulty clock at the  $k^{th}$  tick (adjustment) can be different from the fastest non-faulty clock at the  $(k+1)^{th}$  tick (adjustment). In hardware synchronization, the  $k^{th}$  re-synchronization interval is also called its  $k^{th}$  global clock cycle.

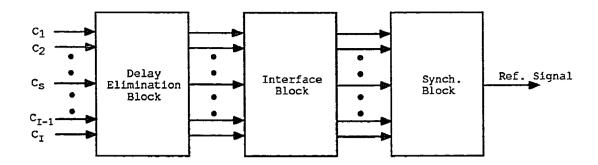

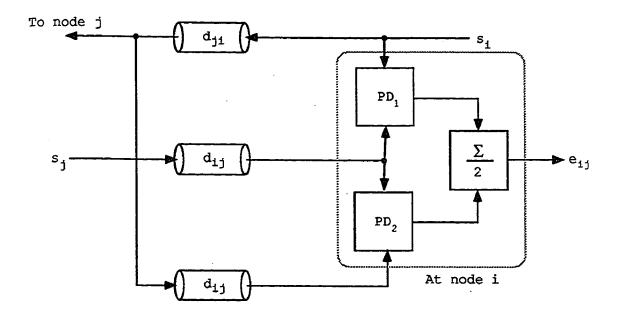

Figure 2.1: Block diagram of the hardware synchronization scheme

# 2.4 A Hardware Synchronization Scheme

Given a distributed system with N nodes, each of which has a clock of its own, the problem is to synchronize all the non-faulty clocks in the system to a specified fault tolerance m. The phase-locked algorithms in [29, 33, 67] solve this problem, but require the transmission delays to be negligible and a large number of interconnections. The effects of transmission delay in phase-locked loops have been studied in great detail in the communication area [41, 70] but not in the presence of Byzantine faults. It is shown below and in [59] that it is easy to incorporate the ideas from the communication area to take into account the presence of both Byzantine faults and non-negligible transmission delays.

# 2.4.1 Elimination of transmission delay effects

A block diagram of the hardware clock synchronization scheme is shown in Figure 2.1. It comprises three basic blocks: the *delay elimination* block, the *interface* block and the *synchronization* block. The delay elimination block receives all the other clocks as inputs and outputs analog voltages<sup>1</sup> proportional to the exact phase difference between the input clocks and its own clock. The interface block converts these analog voltages into a form suitable for the synchronization block. The synchronization block can be any one of the existing hardware synchronization circuits [29, 57, 67] and will not be discussed here. The details of other two blocks are discussed

<sup>1</sup> one for each of the other clocks.

in terms of the following notation.

$s_i$  The clock signal from node i.

$T_{gcc}$  The global clock cycle.

$d_{ij}$  Transmission delay for  $s_i$  to reach node i

$\tau_{ij}$  Phase difference between the clocks at nodes i and j expressed in real time units.

$\delta$  Maximum phase difference between any two non-faulty clocks in the system.

$e_{ij}$  Estimated phase difference at node i between the clocks at nodes i and j.

# The delay elimination block

For clarity of presentation, consider the delay elimination block at node i. The delay elimination block consists of I-1 identical subblocks, i.e., one for each other clock it receives as input. For the interconnection strategy to be put forth later, typically  $I \ll N$ . Consider the subblock corresponding to clock input from node j (see Figure 2.2). It has two phase detectors and an averager. The inputs to the first phase detector,  $PD_1$ , are the clock signals  $s_i$  and  $s_j$ . Since the signal  $s_j$  encounters a delay in reaching node i, the phase difference detected by  $PD_1$  does not represent the true phase difference  $\tau_{ij}$ .

The inputs to the second phase detector,  $PD_2$ , are signals  $s_j$  and  $s_i$  returning from node j. Because of the transmission delays between the two clocks, the signal  $s_i$  returning from node j will be a delayed version of  $s_i$ . Since a delay in time is equivalent to a phase difference, the output of the second phase detector will also depend on the transmission delays. However, if the following four conditions hold, then it is shown in Theorem 2.1 that the average of the outputs of these two phase detectors is proportional to  $\tau_{ij}$  irrespective of the transmission delays.

TD1. The two phase detectors in each subblock have identical gains.

TD2.  $d_{ij} \approx d_{ji}$  for all i, j.

TD3.

$$\delta < \frac{T_{gcc}}{2}$$

.

Figure 2.2: Delay Elimination Block

TD4. For all i, j, and some integer n,

$$nT_{gcc} < d_{ij} < nT_{gcc} + \frac{T_{gcc}}{2} - \delta$$

.

TD1 is a reasonable assumption because the effect of the difference in gains of phase detectors on the worst-case skew is usually much smaller than the effect of transmission delays. TD2 can be easily satisfied if the signals  $s_i$ ,  $s_j$  and their returning signals are routed via almost identical paths. TD3 holds because hardware synchronization schemes achieve lock step synchronization. In fact, in most hardware synchronization schemes  $\delta \ll \frac{T_{gcc}}{2}$ . TD4 should be treated as a design constraint. Even though two clocks can be physically far apart from each other, they should not be allowed to be at arbitrary distances. The physical distance between any two clocks should be such that the transmission delays satisfy TD4.

TD4 is not mentioned in [41], because the output of the phase detector is assumed to <u>always</u> vary linearly with phase difference. This, however, is not realistic since phase differences between  $\tau$  and  $\tau + nT$ , for any integer n, cannot be distinguished from each other by just considering the two signals, i.e., the outputs of phase detectors have a saw-tooth relationship with phase difference rather than a linear relationship [70].

**Lemma 2.1:** If integers  $n_1$  and  $n_2$  satisfy the following two conditions:

(1)

$$\frac{-T_{gcc}}{2} \le (\tau_{ij} + d_{ji} + n_1 T_{gcc}) < \frac{T_{gcc}}{2}$$

(2)

$$\frac{-T_{gcc}}{2} \le (\tau_{ij} - d_{ji} + n_2 T_{gcc}) < \frac{T_{gcc}}{2}$$

then  $n_1 = -n_2$ .

**Proof:** From TD4, there exists an integer n such that  $nT_{gcc} < d_{ji} < nT_{gcc} + \frac{T_{gcc}}{2} - \delta$ . We now show that  $n_1 = -n$  and  $n_2 = n$ .

By definition,  $-\delta \leq \tau_{ij} \leq \delta$ . Hence,

$$nT_{gcc} - \delta < \tau_{ij} + d_{ji} < nT_{gcc} + \frac{T_{gcc}}{2}$$

$$-nT_{gcc} - \frac{T_{gcc}}{2} < \tau_{ij} - d_{ji} < -nT_{gcc} + \delta.$$

(2.1)

Substituting for  $\tau_{ij} + d_{ji}$  and  $\tau_{ij} - d_{ji}$  from the above two equations, it is easy to verify that  $n_1 = -n$  and  $n_2 = n$  satisfy the conditions (1) and (2) (i.e., use TD3). Since integers satisfying (1) and (2) are unique, it follows that  $n_1 = -n_2$ .

Theorem 2.1: If the conditions TD1-TD4 hold, then the output of the averager,  $e_{ij} \approx K\tau_{ij}$  for some constant K.

**Proof:** Let  $v_{ij}^1$  and  $v_{ij}^2$  denote the outputs of the phase detectors  $PD_1$  and  $PD_2$ , respectively. Then for a saw-tooth phase detector [70],

$$v_{ij}^{1} = K_{1}(\tau_{ij} + d_{ij} + n_{1}T_{gcc})$$

(2.2)

$$v_{ij}^{2} = K_{2} \{ \tau_{ij} + d_{ij} - (d_{ij} + d_{ji}) + n_{2} T_{gcc} \}$$

$$= K_{2} (\tau_{ij} - d_{ji} + n_{2} T_{gcc}), \qquad (2.3)$$

where  $K_1$  and  $K_2$  are constants and  $n_1$  and  $n_2$  are integers so chosen that

$$-\frac{T_{gcc}}{2} \leq \tau_{ij} + d_{ji} + n_1 T_{gcc} < \frac{T_{gcc}}{2}$$

$$-\frac{T_{gcc}}{2} \leq \tau_{ij} - d_{ji} + n_2 T_{gcc} < \frac{T_{gcc}}{2},$$

respectively.

From Equations (2.2) and (2.3), the output of the averager is

$$e_{ij} = \frac{1}{2} \left[ K_1(\tau_{ij} + d_{ij} + n_1 T_{gcc}) + K_2(\tau_{ij} - d_{ji} + n_2 T_{gcc}) \right]. \tag{2.4}$$

From TD1,  $K_1 = K_2 = K$ . From Lemma 2.1,  $n_1 = -n_2$ . Substituting these relations in Equation (2.4), we get  $e_{ij} = K\tau_{ij} + \frac{K}{2}(d_{ij} - d_{ji})$ . The theorem then follows from TD2.

# The interface block

The structure of the interface block depends on the synchronization block being used. For illustration, consider the interface block for the hardware synchronization circuit in [29]. In [29], the control voltage to the oscillator depends on whether more than m clocks are faster than the output of the oscillator. From the description of the delay elimination block, it is clear that the clock at node j is faster than the clock at node i if the voltage  $e_{ij}$  is negative. A comparator that outputs a TTL high voltage when the input is negative and a TTL low when the input is positive can be used along with the "greater than m detector" described in [29] to convert the output of the delay elimination block into the desired form.

The complexity and cost of the delay elimination and the interface blocks depend on the number of clock inputs. The following three subsections describe an interconnection strategy and a modified phase locked algorithm in which the number of inputs to each clock is considerably less than the total number of clocks in the system.

# 2.4.2 The interconnection strategy

The total number of interconnections is reduced by grouping the clocks into several clusters and then treating each cluster as a clock unit. Each clock is synchronized by using the phase-locked algorithm not only with all the clocks in its own cluster but also with one clock from each of the other clusters. As a result of this mutual coupling, the clusters remain synchronized with respect to one another and the system as a whole remains well-synchronized.

Let M be the total number of clusters in the system. Let  $p_i$  denote the number of clocks in the  $i^{th}$  cluster. Number the clusters from 1 to M, and also number the clocks in each cluster i from 1 to  $p_i$ . Let  $c_{ij}$  represent the  $j^{th}$  clock of the  $i^{th}$  cluster and let  $q_{ik} \stackrel{\text{def}}{=} [(i-1) \mod p_k] + 1$ . Then each clock in the  $i^{th}$  cluster receives as inputs not only all the clocks from its own cluster but also the  $q_{ik}^{th}$  clock from each cluster  $k \neq i$ . This interconnection for N = 8, M = 4 and  $p_i = 2$  for all i is shown in Table 2.1, where a 1 in row i and column j indicates that the clock corresponding to column j is an input to clock corresponding to row i.

There is no particular sanctity associated with this number  $q_{ik}$ . As long as each clock receives a clock from every other cluster, the algorithm will work. However, the above formula ensures

| ТО              | OUTPUTS FROM |                 |                 |          |          |                 |     |     |

|-----------------|--------------|-----------------|-----------------|----------|----------|-----------------|-----|-----|

|                 | $c_{11}$     | c <sub>12</sub> | c <sub>21</sub> | $c_{22}$ | $c_{31}$ | c <sub>32</sub> | C41 | c42 |

| $c_{11}$        | 1            | 1               | 1               | 0        | 1        | 0               | 1   | 0   |

| $c_{12}$        | 1            | 1               | 1               | 0        | 1        | 0               | 1   | 0   |

| $c_{21}$        | 0            | 1               | 1               | 1        | 0        | 1               | 0   | 1   |

| $c_{22}$        | 0            | 1               | 1               | 1        | 0        | 1               | 0   | 1   |

| c <sub>31</sub> | 1            | 0               | 1               | 0        | 1        | 1               | 1 . | 0   |

| c <sub>32</sub> | 1            | 0               | 1               | 0        | 1        | 1               | 1   | 0   |

| C41             | 0            | 1               | 0               | 1        | 0        | 1               | 1   | 1   |

| $c_{42}$        | 0            | 1               | 0               | 1        | 0        | 1               | 1   | 1   |

Table 2.1: Proposed interconnection scheme for an 8 clock system

that the clock network is symmetric because the formula results in similar fan-out for all the clocks.

# 2.4.3 Modification of the phase-locked algorithm

There are two main differences between the above interconnection strategy and the one in [33]:

- A given clock may receive inputs from clocks to which its own output is not connected.

This was not possible in [33], because every clock received inputs from every other clock in the system.

- Different clocks could receive different number of inputs. This again was not possible in [33], since every clock received exactly N-1 inputs, where N is the total number of clocks in the system.

These two differences cause a minor change in the phase-locked algorithm, since a reference signal is generated for each clock based only on the inputs it receives. That is, if a clock receives I inputs (including itself), then it assumes there are I clocks in the system and functions accordingly. If the maximum number of faults to be tolerated is m, then it is shown in [33] that if (i) I > 3m and (ii) the reference signal is generated as follows, then the non-faulty clocks will remain synchronized. Each clock first orders all the inputs it received in the order of arrival of

the clock ticks. This ordered set is called the *tick sequence* of the corresponding clock. Let x be the position of its own clock in its tick sequence. Then the reference signal chosen by this clock is the  $f_x(I)^{th}$  clock (excluding itself) in its tick sequence where  $f_x(I)$  is any function satisfying one of the following conditions [33]:

- $m+1 \le f_x(N) \le N-m-1$ , for all x=1,...,N

- $f_x(N) \ge m 1 + f_{N-m}(N)$ , for all  $x \le m + 1$ ,

- $f_{N-m}(N) \le f_x(N) \le f_{m+1}(N)$ , for all m+1 < x < N-m,

- $f_i(N) \leq f_j(N)$  iff  $i \leq j$ .

This implies that if different clocks in the system receive different number of inputs then they will have a different function for generating the reference signal. This fortunately has no effect on the synchronizing capabilities of the network.

# 2.4.4 Minimization of the number of interconnections

Assume for the time-being that all the clusters have the same size, p. This implies  $M \cdot p = N$ . The goal is to minimize the total number of interconnections  $J \equiv Mp(p-1) + Mp(M-1) = N(M+p-2)$  subject to the required level of fault tolerance, which can be stated as  $M+p-2 \geq 3m$  from the Byzantine Generals paradigm and the interconnection strategy. Substituting for p in M+p-2 from N=Mp and differentiating with respect to M, it is easy to show that M+p-2 increases with M. Therefore both the total number of interconnections and the fault tolerance of the network increase with M. So minimizing J is equivalent to minimizing M. By solving for M in the fault tolerance condition and combining it with the above result, we can get a unique value for M that minimizes the total number of interconnections while satisfying the fault tolerance requirement.

However, the assumption that all clusters are of the same size is not appropriate for all values of N. For instance, if N were a prime number, then it would not be possible to find two factors M and p other than N and p. This means that if we restrict ourselves to clusters of a single size, only fully connected networks are possible. On the other hand, any N can be decomposed into clusters of two different sizes, say  $p_1$  and  $p_2$ . This will result in fewer interconnections than a

fully connected network. There is no need to consider clusters of more than two sizes due to the reasons outlined below.

As  $p_1$  and  $p_2$  decrease in magnitude, the network tends to change towards a fully connected network, i.e., the fault tolerance of the network increases and so does the total number of interconnections. These are the two opposing factors which determine the values of  $p_1$  and  $p_2$ . Had there been no fault tolerance condition the minimum number of interconnections would have occurred at  $p_1 = p_2 = \sqrt{N}$ . From symmetry considerations, we know that even under fault tolerance conditions the minimum number of interconnections will occur when  $p_1 = p_2$ . But since for any general N it may not be possible to find a  $p_1$  and  $p_2$  such that  $p_1 = p_2$ , the minimum number of interconnections occur when  $p_1 - p_2 = 1$ . Since any N can be decomposed into this form, at worst, it is necessary to have clusters of two different sizes  $p_1$  and  $p_1 - 1$ . An algorithm to partition the clocks into clusters of two different sizes such that the total number of interconnections is minimized is described below.

Let the N clocks be partitioned into  $M_1$  clusters of  $p_1$  clocks each and  $M_2$  clusters of  $p_2$  clocks each, where  $p_1 \ge p_2$ . This implies  $M_1p_1 + M_2p_2 = N$ . Number the clusters with  $p_1$  clocks (henceforth referred to as CP1) from 1 to  $M_1$  and the clusters with  $p_2$  clocks (CP2) from  $M_1 + 1$  to  $M_1 + M_2$ . Also number the clocks in a given cluster from 1 to  $p_1$  or 1 to  $p_2$  correspondingly.

Let  $q_{i1} = [(i-1) \bmod p_1] + 1$  and  $q_{i2} = [(i-1) \bmod p_2] + 1$ . Then each clock in cluster i receives the  $q_{i1}^{th}$  clock from each CP1 and  $q_{i2}^{th}$  clock from each CP2 in addition to all the clocks from its own cluster. The problem is to determine  $M_1$ ,  $p_1$ ,  $M_2$ , and  $p_2$  that minimize the total number of interconnections and meet the specified fault tolerance requirement. The solution to this problem is more difficult than the case of single cluster size because there are three independent variables  $M_1$ ,  $p_1$ ,  $p_2$  as opposed to only one.

The total number of interconnections in this scheme can be derived as follows.

- The total number of inputs to each clock in CP1:  $M_1 + M_2 + p_1 1$ .

- The total number of inputs to each clock in CP2:  $M_1 + M_2 + p_2 1$ .

Consequently, the total number of interconnections

$$J = M_1 p_1 (M_1 + M_2 + p_1 - 1) + M_2 p_2 (M_1 + M_2 + p_2 - 1)$$

$$= N (M_1 + M_2 - 1) + M_1 p_1^2 + M_2 p_2^2.$$

The decomposition problem can then be formally stated as:

**Problem D:** Determine non-negative integers  $M_1$ ,  $p_1$ ,  $M_2$ ,  $p_2$  which minimize

$$J = N(M_1 + M_2 - 1) + M_1 p_1^2 + M_2 p_2^2$$

subject to

$$M_1p_1 + M_2p_2 = N$$

$M_1 + M_2 + p_2 - 2 \ge 3m$

$p_1 - p_2 \ge 0$

$p_1 \le 2(M_1 + M_2 - 1)$ .

Since there are only finitely many integers between 0 and N, there are only finitely many possible solutions for  $M_1$ ,  $M_2$ ,  $p_1$ ,  $p_2$ . Thus, there definitely exists an integer solution to the above problem. For small N we can determine the solution by enumerating all the possible solutions and choosing the one that gives the minimum value for J. For larger N we can take recourse to non-linear integer programming methods [24].

### 2.4.5 Proof of correctness

In this section, it is shown that the above interconnection scheme coupled with the modified phase-locked algorithm ensures synchronization of a N clock system in the presence of m faults when  $N \ge 3m+1$ .

Let CK denote the set of clocks in the system. Consider a clock from this set. There are two possibilities: either this clock is connected only to all the clocks in its own cluster or it is also connected to at least one cluster other than its own. CK can therefore be decomposed into two subsets A and B such that  $A \cap B = \emptyset$ , where A is the set of all clocks which are connected to at least one cluster other than its own, and B is the set of all clocks connected only to its own cluster. Let  $CL_i$ ,  $i \in L \equiv \{1, 2, ..., M\}$ , be one of the M clusters in the system. Due to the interconnection strategy adopted, for any cluster pair,  $CL_i$  and  $CL_j$ , there is one and only one clock in  $CL_i$  which serves as an input to all the clocks in  $CL_j$ . Denote this clock by the ordered pair (i,j). There is one more clock link between  $CL_i$  and  $CL_j$ , but this clock is from  $CL_j$  to  $CL_i$ , i.e., it is the input to  $CL_i$  from  $CL_j$ , and so will be denoted by  $(j,i) \in CL_j$ . Also, every

such ordered pair of clusters uniquely represents a clock in set A. On the other hand, a clock in set A can have more than one such ordered pair representation but definitely has one such representation. Based on this observation, partition the clocks into four groups with respect to any given cluster,  $CL_j$ , as follows:

$IN_j \equiv \{i: i \in L, (i, j) \text{ is non-faulty}\}$   $IF_j \equiv \{i: i \in L, (i, j) \text{ is faulty}\}$   $ON_j \equiv \{i: i \in L, (j, i) \text{ is non-faulty}\}$   $OF_i \equiv \{i: i \in L, (j, i) \text{ is faulty}\}.$

If i=k, then  $c_{ij}$  and  $c_{kl}$  are two non-faulty clocks of the same cluster and they are assumed to be  $\delta$ -synchronized. Theorem 2.2 shows that when  $i \neq k$ , the interconnection scheme is such that  $c_{ij}$  and  $c_{kl}$  are  $3\delta$ -synchronized irrespective of the location of the faults in the system. Informally, the idea of the proof is to show that irrespective of the location of the faults, there exists a non-faulty link from either  $CL_i$  to  $CL_k$  or vice versa with at most two hops.

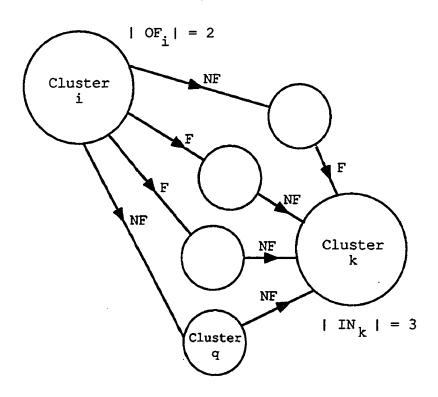

**Lemma 2.2:** For any two clusters  $CL_i$  and  $CL_k$  satisfying  $|OF_i| < |IN_k|$ , there exists a nonfaulty path from  $CL_i$  to  $CL_k$  with at most two hops. See Figure 2.3 for an illustration. In the figure,  $|\bullet|$  denotes the cardinality of a set.

**Proof:** First, suppose that the clock (i, k) is non-faulty. Then, irrespective of the location of the faults there is a direct path from  $CL_i$  to  $CL_k$  containing exactly one hop. Therefore, the more interesting case occurs when the clock (i, k) is faulty. In this case the lemma is proved via a contradiction.

Assume that there exists no cluster  $CL_q \in IN_k$  such that (i,q) is non-faulty. This means for any cluster  $CL_s \in IN_k$  the clock (i,s) is faulty. In other words, there are at least  $|IN_k|$  faulty clock outputs from  $CL_i$ , i.e.,  $|OF_i| \ge |IN_k|$ , a contradiction.

Theorem 2.2: Let  $c_{ij}$  and  $c_{kl}$  be any two non-faulty clocks in the system. Also let  $\delta$  be the maximum skew that can arise between any two non-faulty clocks in the same cluster as a result of applying the phase-locked algorithm. Then,  $|c_{ij} - c_{kl}| \leq 3\delta$  for all i, j, k, and l in  $L \equiv \{1, 2, \ldots, M\}$  under the condition  $p_{max} \leq 2M - 2$ , where  $p_{max} = \max\{p_1, p_2, \ldots, p_M\}$ .

Figure 2.3: Illustration of case  $|OF_i| < |IN_k|$  for Lemma 2.2

**Proof:** Let  $|IF_k| = x$  and let m be the maximum number of faults that needs to be tolerated. Since there are a total of M clusters in the system, it follows from the interconnection strategy that the total number of external inputs to any cluster is M-1. In other words,

$$|IN_k|=M-x-1$$

, or  $|IF_k|+|IN_k|=M-1$  for all  $k\in L$ .

Consider the following two cases.

Case 1:

$$|OF_i| < \min \{M - x - 1, m + 1\}.$$

Since  $|OF_i| < M - x - 1 = |IN_k|$ , by Lemma 2.2 there exists a cluster  $CL_q$  such that clocks (i, q) and (q, k) are both non-faulty. From the triangle inequality we get,

$$|c_{ij}-c_{kl}| \leq |c_{ij}-(i,q)|+|(i,q)-(q,k)|+|(q,k)-c_{kl}| \leq 3\delta.$$

Case 2:

$$M-x-1 \leq |OF_i| \leq m$$

.

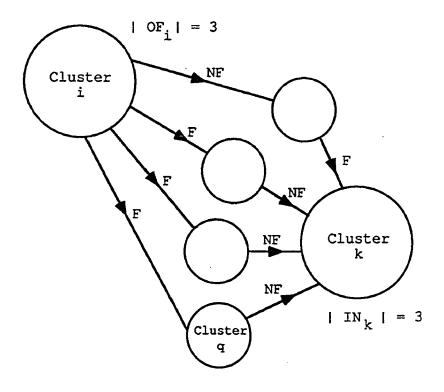

In this case it is possible that there is no  $CL_q \in IN_k$  such that (i,q) is non-faulty, i.e., there is no non-faulty link from  $CL_i$  to  $CL_k$  (for example, see Figure 2.4). In such a case, it is shown that there is always a non-faulty path from  $CL_k$  to  $CL_i$ .

Let  $r \equiv \left\lceil \frac{M}{p_{min}} \right\rceil$  where  $\lceil x \rceil$  is the smallest integer not less than x and  $p_{min} = \min \{p_1, p_2, \ldots, p_M\}$ . Then, according to the interconnection strategy, every clock in the system could go to at most r different clusters. Using this along with the hypothesis  $M-x-1 \leq |OF_i|$ , there are at least  $\left\lceil \frac{M-x-1}{r} \right\rceil$  faulty clocks in  $CL_i$ . Thus, there are at most  $m-\left\lceil \frac{M-x-1}{r} \right\rceil$  faulty clocks in the inputs to  $CL_i$ , i.e.,

$$|IF_i| \le m - \left\lceil \frac{M-x-1}{r} \right\rceil, \quad \text{or} \quad |IN_i| \ge M-1-m + \left\lceil \frac{M-x-1}{r} \right\rceil.$$

(2.5)

Since  $|IF_k| = x$ , there are at most m - x faulty clocks in  $CL_k$  and, thus,

$$|OF_k| \le r(m-x). \tag{2.6}$$

If possible let there be no non-faulty path from  $CL_k$  to  $CL_i$  of length less than or equal to two hops. Then, from Lemma 2.2,  $|OF_k| \ge |IN_i|$ . Therefore, from Equations (2.5) and (2.6),

$$r(m-x) \ge (M-1)-m+\left\lceil \frac{(M-x-1)}{r} \right\rceil \ge (M-1)-m+\frac{(M-x-1)}{r}$$

or  $r^2 \cdot m + r \cdot m \ge (r+1)(M-1)+(r^2-1)x$ .

Figure 2.4: Illustration of the case  $|OF_i| \ge |IN_k|$  for Theorem 2.2

Since  $x \leq m$ , it follows that  $m \geq M-1$ . Therefore, the maximum number of inputs to any clock is  $M+p_{max}-1$  where  $p_{max}=\max\{p_1,p_2,\ldots,p_M\}$ . From the Byzantine Generals paradigm  $\frac{M+p_{max}-1}{3}>m$ , leading to

$$M-1 \le m < \frac{M+p_{max}-1}{3}$$

or  $p_{max} > 2M-2$ .

which contradicts the hypothesis. In other words,  $|OF_k| < |IN_i|$ . Then by Lemma 2.2 there exists at least one  $q \in IN_i$  such that the clock (k,q) is non-faulty. Applying triangle inequality, for all i, j, k, and l

$$|c_{kl}-c_{ij}| \leq |c_{kl}-(k,q)| + |(k,q)-(q,i)| + |(q,i)-c_{ij}| \leq 3\delta.$$

The condition  $p_{max} \leq 2M-2$  in the above theorem implies that the connectivity is sufficiently large to ensure a good synchronization. The maximum fault tolerance is achieved in a fully connected network, i.e., when  $p_{max} = 1$  and M = N > 1, in which case case the above condition is satisfied. In order to reduce the number of interconnections it is necessary to compromise on the maximum number of faults that can be tolerated. As shown earlier it is sufficient to have  $p_{max} \leq \sqrt{N}$  to ensure the least number of interconnections under any fault tolerance specification when all the clusters are of the same size. The condition  $p_{max} \leq 2M-2$  is a generalization of the condition  $p_{max} \leq \sqrt{N}$  because  $p_{max} \leq \sqrt{N}$  implies  $p_{max} \leq 2M-2$ .

## 2.4.6 Numerical example

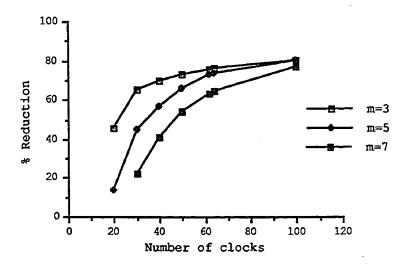

The following results were obtained by solving Problem D using simple enumeration techniques. Table 2.2 illustrates the variation in the total number of interconnections with respect to the size of the system when the fault tolerance requirement is kept constant. The table also gives the percentage reduction in the number of interconnections as compared to a fully connected network. The plot of the variation in percentage reduction with respect to the size of the system and hence with respect to the number of clocks is given in Figure 2.5.

Figure 2.5 indicates that for a given fault tolerance condition the total number of interconnections increases proportionately to the size of the system. This is because when the size increases, the number of clocks in the system increases, and so more interconnections are needed to keep

| N   | m | $M_1$ | $p_1$ | $M_2$ | $p_2$ | J    | % Reduction |

|-----|---|-------|-------|-------|-------|------|-------------|

| 20  | 3 | 2     | 3     | 7     | 2     | 206  | 45.79       |

| 30  |   | 6     | 5     | 0     | 0     | 300  | 65.52       |

| 40  |   | 2     | 6     | 4     | 7     | 468  | 70.00       |

| 50  |   | 1     | 8     | 6     | 7     | 658  | 73.14       |

| 62  |   | 2     | 7     | 6     | 8     | 916  | 75.78       |

| 64  |   | 1     | 8     | 7     | 8     | 960  | 76.19       |

| 100 |   | 10    | 10    | 0     | 0     | 1900 | 80.19       |

| 20  | 5 | 4     | 2     | 12    | 1     | 328  | 13.68       |

| 30  |   | 1     | 2     | 14    | 2     | 480  | 44.83       |

| 40  |   | 5     | 2     | 10    | 3     | 670  | 57.05       |

| 50  |   | 6     | 3     | 8     | 4     | 832  | 66.04       |

| 62  | İ | 2     | 6     | 10    | 5     | 1004 | 73.45       |

| 64  |   | 4     | 6     | 8     | 5     | 1048 | 74.01       |

| 100 |   | 10    | 10    | 0     | 0     | 1900 | 80.19       |

| 20  | 7 | -     | -     | -     | -     | -    | -           |

| 30  |   | 14    | 1     | 8     | 2     | 676  | 22.30       |

| 40  | ļ | 4     | 1     | 18    | 2     | 916  | 41.28       |

| 50  |   | 8     | 3     | 13    | 2     | 1124 | 54.12       |

| 62  |   | 2     | 4     | 18    | 3     | 1372 | 63.72       |

| 64  |   | 4     | 4     | 16    | 3     | 1424 | 64.68       |

| 100 |   | 8     | 5     | 10    | 6     | 2260 | 77.17       |

Table 2.2: Variations in number of interconnections with size of the system

Figure 2.5: % Reduction over a fully connected network versus size of the system

them synchronized. However, while the total number of interconnections increases, the percentage reduction in the total number of interconnections also increases with the size of the system. This is significant because the fault tolerance condition will not usually increase proportionately with the size of the system. In such a case, reduction in the total number of interconnections will be one of the main concerns and our scheme works well in that situation.

Another aspect that is clear from Table 2.2 is that reductions up to 80% can be achieved for relatively less stringent fault tolerance condition. However, under those conditions the interconnection scheme in [62] requires fewer interconnections as compared to the scheme here (see Table 2.3). But as the fault tolerance specification becomes more stringent the percentage difference between the number of interconnections in both schemes drops rapidly to a very low value and then remains almost constant through the entire range. This aspect is clearly depicted by the plots in Figure 2.6. In other words, the scheme in [62] is only marginally better than the scheme put forth here under almost all fault tolerance specifications.

# 2.4.7 Comments

The above hardware synchronization scheme provides a tradeoff between fault tolerance and the total number of interconnections. This scheme can be used to determine a symmetric clock

| N        | m  | $M_1$ | $p_1$ | $M_2$ | $p_2$ | J    | $J_{FTMP}$ | %Increase |

|----------|----|-------|-------|-------|-------|------|------------|-----------|

| 20       | 2  | 5     | 4     | 0     | 0     | 160  | 120        | 33.30     |

|          | 3  | 2     | 3     | 7     | 2     | 206  | 180        | 14.44     |

|          | 4  | 6     | 1     | 7     | 2     | 274  | 240        | 14.17     |

|          | 5  | 4     | 2     | 12    | 1     | 328  | 300        | 9.33      |

|          | 6  | 20    | 1     | 0     | 0     | 380  | 360        | 5.55      |

| 62       | 3  | 2     | 7     | 6     | 8     | 916  | 558        | 64.16     |

|          | 5  | 2     | 6     | 10    | 5     | 1004 | 930        | 7.90      |

|          | 7  | 2     | 4     | 18    | 3     | 1372 | 1302       | 5.38      |

|          | 8  | 10    | 2     | 14    | 3     | 1592 | 1488       | 6.99      |

|          | 9  | 8     | 3     | 19    | 2     | 1760 | 1674       | 5.14      |

|          | 12 | 12    | 1     | 25    | 2     | 2344 | 2232       | 5.01      |

|          | 18 | 7     | 2     | 48    | 1     | 3424 | 3348       | 2.27      |

|          | 20 | 20    | 1     | 0     | 0     | 3782 | 3720       | 1.67      |

| 64       | 3  | 8     | 8     | 0     | 0     | 960  | 576        | 66.67     |

|          | 5  | 4     | 6     | 8     | 5     | 1048 | 960        | 9.17      |

|          | 7  | 4     | 4     | 16    | 3     | 1424 | 1344       | 5.95      |

|          | 9  | 10    | 3     | 17    | 2     | 1822 | 1728       | 5.44      |

|          | 12 | 10    | 1     | 27    | 2     | 2422 | 2304       | 5.12      |

|          | 18 | 9     | 2     | 46    | 1     | 3538 | 3456       | 2.37      |

| <u> </u> | 21 | 64    | 1     | 0     | 0     | 4032 | 4032       | 0.00      |

| 100      | 3  | 10    | 10    | 0     | 0     | 1900 | 900        | 111.11    |

|          | 6  | 10    | 10    | 0     | 0     | 1900 | 1800       | 5.55      |

|          | 10 | 16    | 3     | 13    | 4     | 3152 | 3000       | 5.07      |

|          | 15 | 10    | 3     | 35    | 2     | 4630 | 4500       | 2.88      |

|          | 20 | 22    | 1     | 39    | 2     | 6178 | 6000       | 2.97      |

|          | 25 | 24    | 2     | 52    | 1     | 7648 | 7500       | 1.97      |

|          | 30 | 9     | 2     | 82    | 1     | 9118 | 9000       | 1.31      |

| L        | 33 | 100   | 1     | 0     | 0     | 9900 | 9900       | 0.00      |

Table 2.3: Variations in number of interconnections with fault tolerance specification

31

Figure 2.6: % Increase versus specified fault tolerance

network that requires a near minimal number of interconnections for any fault tolerance specification. In large systems, up to 80% reduction can be achieved in the total number of interconnections as compared to other hardware solutions with worst-skews in the order of 30-50 ns.

In spite of this considerable reduction, the cost of additional hardware can be substantial for many applications. The scheme requires a network of clocks that is different from the interconnection network between the nodes of the system. In addition, each clock is required to have two phase-detectors for every clock input and some circuitry to select a reference signal and adjust the local clock.

For systems that cannot afford the cost of additional hardware in the above approach, a software synchronization scheme is proposed below. This scheme strikes a balance between the hardware requirement and the clock skews attainable. Unlike other software solutions, the guaranteed worst-case skews in this scheme can be made insensitive to the message transit delay in the system. The scheme is also particularly suitable for large partially connected distributed systems with topologies that support simple broadcast algorithms. Examples of such topologies include the hypercube and the mesh interconnection structures.

## 2.5 A Software Synchronization Scheme

The scheme proposed here is similar to the interactive convergence algorithm (CNV) in [36]. The differences arise mainly because CNV is intended for a fully connected system as opposed to a partially connected system like the hypercube [53] or the mesh topologies [1]. Although CNV could be used in a partially connected system, it is not well suited for such a system since the worst-case skews in CNV are greater than the maximum message transit delay in the system. In contrast, the worst-case skews in the scheme below are orders of magnitude smaller than the maximum time required for a reliable broadcast and they do not depend on this maximum time beyond a certain limit.

Algorithm CNV assumes that the clocks are initially synchronized and that they drift apart only by a bounded amount during a resynchronization interval. Each node executes a clock process (CP) that is responsible for maintaining a time base for all the activities on that node. In every resynchronization interval, each CP reads the value of the clock at all other nodes. If the value of a clock read differs from the clock at its node by an amount greater than a threshold, CP replaces that value by its own clock value. CP then computes the average of all such values and sets the local clock to that average. In [36], it is shown that this algorithm can achieve synchronization, and requires a minimum of 3m + 1 nodes to tolerate m faults.

Three major problems arise when this algorithm is used in a distributed system that is not fully connected. First, the clock message received at a node may be corrupted by a faulty intermediate node. Second, the queueing delay for clock messages may cause a substantial difference between the real time at which a CP sends the clock value and the real time at which another CP receives that message. Therefore, subtracting the clock value in the received message from the current clock value will not reflect the actual skew that exists between the clocks of the two nodes. This problem is aggravated when system is partially connected because the clock message has to be relayed through intermediate nodes. Third, there may be a delay between the receipt of a clock message from the network and the time at which it is processed. A similar delay is possible between the time at which a CP sends the message and the time at which the message is placed on the network. The first problem is eliminated in the proposed scheme by using a broadcast algorithm that delivers multiple copies of the message to all CPs through node-disjoint paths.

The second problem is reduced by requiring the CP at each intermediate node to append to the message the delay (according to the local clock) incurred at that node. The third problem is handled by recording the time at which a clock message is sent or received.

In the proposed scheme, a CP broadcasts the local clock value to all other CPs at a specified time in the resynchronization interval according to its clock. The broadcast algorithm is such that all CPs receive multiple copies of the clock message through node-disjoint paths. The number of copies used in the broadcast algorithm depends on the maximum number of faults to be tolerated and the fault model for the system. When a CP receives a clock message sent by some other CP, it records the time (according to its local clock) at which the message was received. Then, in accordance with the broadcast algorithm, it relays the message to other CPs. Before relaying the message, it appends to the message the time elapsed (according to its own clock) since the receipt of the message. At the end of a resynchronization interval, it computes the skews between the local clock and the clock of the source node for each one of the copies it has received. It then selects the  $(m+1)^{th}$  largest value as an estimate of the skew between the two clocks. The average of the estimated skews over all nodes is used as the correction to the local clock. As in CNV a minimum of 3m+1 nodes are required to tolerate m Byzantine faults.

The above steps are explained in terms of four concurrent tasks: CLOCK\_SEND, CLOCK\_RELAY, CLOCK\_RECEIVE and CLOCK\_CORRECTION. An efficient implementation of these tasks requires some hardware support and a reliable broadcast mechanism.

#### 2.5.1 Hardware support

A clock message contains the following information: the node at which the broadcast was initiated (namely, the initiator), the node from which the message was most recently relayed (namely, the immediate sender), and five words  $W_1, W_2, \ldots, W_5$  shown below. The relative ordering of these words in the message depends on the format being used in the system.

$W_1$ : Clock time of the initiator when this message was transmitted.

$W_2$ : Clock time of the immediate sender when it received this message.

$W_3$ : Clock time of the immediate sender when it relayed this message.

$W_4$ : Accumulated transit delay not counting the delay at the immediate sender.

$W_5$ : The time on the local clock when this message was received.