# Thermal and QoS-Aware Embedded Systems

by

Youngmoon Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2019

### Doctoral Committee:

Professor Kang G. Shin, Chair Assistant Professor Mosharaf Chowdhury Professor Wei Lu Professor Thomas F. Wenisch Youngmoon Lee

ymoonlee@umich.edu

ORCID iD: 0000-0002-6393-2994

© Youngmoon Lee 2019

All Rights Reserved

To my wife Jinwoo and my parents Taeho and Hyesook

for their unwavering love and support

### ACKNOWLEDGEMENTS

When I look back on the 5 years of my Ph.D. program, I now realize how much I have been given. I was given an endless time to sit down and think that made me an independent thinker. Furthermore, I was given another chance upon failures, which made me never give up on challenges. My most sincere gratitude goes to my advisor Kang G. Shin, who has been extremely patient in fostering my independent thinking. I would also like to thank my collaborator Mosharaf Chowdhury who has been my hands-on mentor. I will never forget his patience and never giving up spirit.

I am indebted to all the members of Real-Time Computing Lab (RTCL) where I learned a lot from each of these independent thinkers. I would especially like to acknowledge my colleagues Sunmin, Liang, and Hoonsung. We spent an enormous amount of time shaping ideas and refining them into research problems and solutions. I would also like to thank Karen, Xiaoen, Krishina, Huan, Kassem, Kyongtak, Yuchih, Seunghyun, Arun, Dongyao, Taeju, Juncheng, Chunyu, Mert, Duc, Tim, Hsunwei, Youssef, Suining, Hamed, Sunhyun, Daehan, Jiaqing, and Haichuan.

I would like to express my gratitude to my family, especially my wife, Jinwoo. She has been always with me when I was struggling the most. Thank you for trusting me for the 7 years we have spent together. In addition, I appreciate my parents - Taeho and Hyesook - for their unwavering love and support.

My acknowledgments also go to all the people who helped me during my graduate studies. Finally, I wish to acknowledge the support of the National Science Foundation and the South Korean government with my graduate fellowship.

# TABLE OF CONTENTS

| DEDICATIO   | <b>V</b>                                                       | ii                          |

|-------------|----------------------------------------------------------------|-----------------------------|

| ACKNOWLE    | DGEMENTS                                                       | iii                         |

| LIST OF FIG | URES                                                           | vii                         |

| LIST OF TAI | BLES                                                           | Х                           |

| ABSTRACT    |                                                                | xi                          |

| CHAPTER     |                                                                |                             |

| I. Intro    | luction                                                        | 1                           |

| 1.1         | Thermal Challenges                                             | 2                           |

| 1.2         | 1.1.2 Low Temperature                                          | 3<br>4<br>4                 |

|             | 1.2.2 Hardware Thermal Variabilities                           | 4                           |

| 1.3<br>1.4  | State of the Art Thesis Statement and Contributions  1.4.1 BPM | 5<br>7<br>8<br>8<br>9<br>10 |

| II. BPM: E  | attery-Aware Power Management                                  | 11                          |

| 2.1<br>2.2  | Introduction                                                   | 11<br>14<br>14<br>16        |

| 2.3        | Causes of Unexpected Device Shutoffs                       |

|------------|------------------------------------------------------------|

| 2.4        | Fixes for Unexpected Device Shutoffs                       |

|            | 2.4.1 Overview                                             |

|            | 2.4.2 Profiling Batteries During Charging 23               |

|            | 2.4.3 Regulating Battery Voltage During Discharging 28     |

| 2.5        | BPM Implementation                                         |

| 2.6        | Evaluation                                                 |

|            | 2.6.1 Methodology                                          |

|            | 2.6.2 Preventing Unexpected Device Shutoffs                |

|            | 2.6.3 Performance—Operation Time Tradeoff 39               |

|            | 2.6.4 BPM with Different Temperature and Battery Cycles 42 |

| 2.7        | Related Work                                               |

| 2.8        | Conclusion                                                 |

|            |                                                            |

| III. eTEC: | Efficient Thermoelectric Cooling                           |

|            |                                                            |

| 3.1        | Introduction                                               |

| 3.2        | Related Work                                               |

| 3.3        | Motivation                                                 |

| 3.4        | System Thermal Model                                       |

|            | 3.4.1 TEC Cooling Model                                    |

|            | 3.4.2 Processor Power Model                                |

|            | 3.4.3 System Thermal Model                                 |

| 3.5        | Processor Thermal Management                               |

|            | 3.5.1 Thermal Model Identification                         |

|            | 3.5.2 TEC Optimization                                     |

|            | 3.5.3 Dynamic TEC Control 57                               |

| 3.6        | Evaluation                                                 |

| 3.7        | Conclusion                                                 |

|            |                                                            |

| IV. RT-TR  | M: Real-time Thermal-Aware Resource Management 64          |

|            |                                                            |

| 4.1        | Introduction                                               |

| 4.2        | Related Work                                               |

| 4.3        | Target System, Challenges, and Solution Overview 68        |

|            | 4.3.1 Target System                                        |

|            | 4.3.2 Problem Statement and Motivation                     |

|            | 4.3.3 Overview of the Proposed Approach                    |

| 4.4        | Task-Level Power Model                                     |

|            | 4.4.1 Task-Level Dynamic Power Model                       |

|            | 4.4.2 Empirical Model Validation                           |

| 4.5        | Adaptive Parameter Assignment                              |

|            | 4.5.1 Parameter Assignment                                 |

|            | 4.5.2 Runtime Parameter Adaptation                         |

| 4.6        | Online Idle-time Scheduling 82                             |

| 4.7       | Evaluation                                            | 88  |

|-----------|-------------------------------------------------------|-----|

| 4.8       | Discussion                                            | 95  |

| 4.9       | Conclusion                                            | 96  |

| V. RT-TAS | S: Real-time Thermal-Aware CPUs-GPU Scheduling .      | 97  |

| 5.1       | Introduction                                          | 97  |

| 5.2       | Related Work                                          | 100 |

| 5.3       | Motivation                                            | 101 |

|           | 5.3.1 Target System                                   | 102 |

|           | 5.3.2 Thermal Characteristics of CPUs–GPU Platforms . | 102 |

|           | 5.3.3 Why Thermal-Aware Task Scheduling?              | 104 |

| 5.4       | CPUs-GPU System Model                                 | 106 |

|           |                                                       | 106 |

|           | 5.4.2 CPU and GPU Power-dissipation Model             | 108 |

|           | 5.4.3 Platform's Thermal Model                        | 109 |

|           | 5.4.4 Parameter Identification and Validation         | 110 |

| 5.5       | Thermal-Aware Scheduling                              | 112 |

|           | 5.5.1 Thermally-Balanced Assignment                   | 112 |

|           | 5.5.2 CPU-GPU Co-Scheduling                           | 118 |

| 5.6       | Evaluation                                            | 124 |

|           | 5.6.1 Methodology                                     | 124 |

|           | 5.6.2 Effectiveness at Reducing Temperature           | 126 |

|           | 5.6.3 Evaluation with Different Task Sets             | 129 |

| 5.7       | Conclusion                                            | 131 |

| VI. Concl | lusion and Future Directions                          | 133 |

| 6.1       | Contributions, Limitations, and Lessons Learned       | 133 |

| 6.2       | ,                                                     | 135 |

| BIBLIOGRA | PHY                                                   | 137 |

# LIST OF FIGURES

| Figure |                                                                                                                                                             |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1    | Thermal challenges in embedded systems threatening system                                                                                                   |

|        | reliability and user's safety                                                                                                                               |

| 2.1    | Battery-aware power management middleware                                                                                                                   |

| 2.2    | Equivalent circuit model of a mobile device: the device will shut off when the battery voltage $V_b$ is lower than the minimum level required by the device |

| 2.3    | The OCV-SoC relationship of batteries                                                                                                                       |

| 2.4    | Operating a Nexus 5X phone: playing a video, idling, and then playing a game until shutoff                                                                  |

| 2.5    | Battery impedance rises as temperature falls                                                                                                                |

| 2.6    | Unexpected shutoff of a Nexus 5X smartphone in a cold ambient temperature                                                                                   |

| 2.7    | Voltage drop at shutoff vs. the average voltage drop and SoC at shutoff of a Nexus 5X battery                                                               |

| 2.8    | Battery impedance and SoC when different mobile devices shut off.                                                                                           |

| 2.9    | BPM profiles the device battery during charging and regulates the voltage drop during discharging                                                           |

| 2.10   | BPM's duty-cycled charging vs. standard CCCV charging                                                                                                       |

| 2.11   | Estimating battery parameters using battery voltage during resting.                                                                                         |

| 2.12   | Battery parameters estimated at different SoC levels for the 1st, 100th, and 200th charging cycles                                                          |

| 2.13   | Validating the temperature-dependency model over 100 cycles with Nexus 5X battery                                                                           |

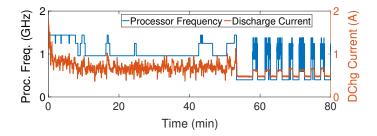

| 2.14   | The processor incurs a burstier discharge current than other components                                                                                     |

| 2.15   | Component-specific discharge currents                                                                                                                       |

| 2.16   | Processor frequency variations during the phone's real-life usage                                                                                           |

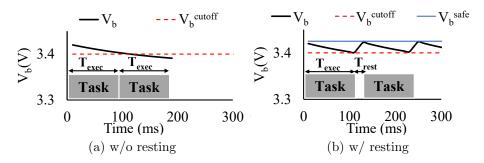

| 2.17   | Battery voltage with and without inserting rest periods between task executions                                                                             |

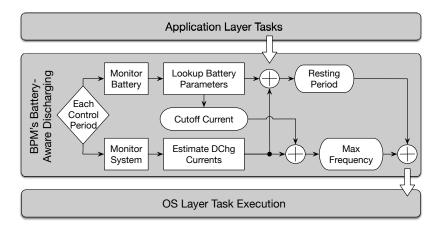

| 2.18   | Control flow of BPM's battery-aware discharging management                                                                                                  |

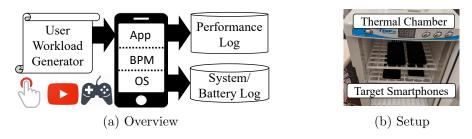

| 2.19   | Experimental setup                                                                                                                                          |

| 2.20         | Operating a Nexus 5X (143rd cycle) until it shuts off, with and without BPM                                                                                                                     | 37       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.21         | BPM prevents unexpected device shutoffs and extends device operation, especially for aged devices                                                                                               | 38       |

| 2.22         | BPM (a) reduces the peak discharge current by (b) limiting the                                                                                                                                  | 30       |

| ว วว         | processor frequency, thus (c) achieving extended device operation                                                                                                                               | 39<br>40 |

| 2.23<br>2.24 | Performance and operation time tradeoff                                                                                                                                                         | 40       |

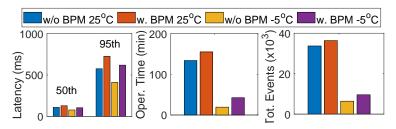

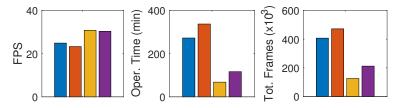

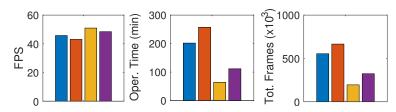

|              | UI latency/operation time/total events                                                                                                                                                          | 41       |

| 2.25         | Video FPS/operation time/total frames                                                                                                                                                           | 41       |

| 2.26<br>2.27 | Game FPS/operation time/total frames                                                                                                                                                            | 41       |

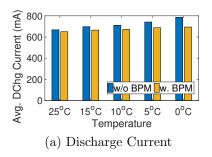

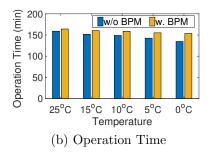

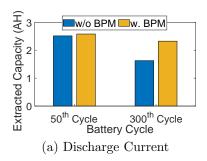

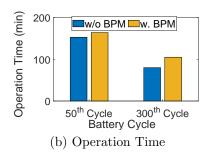

| 2.28         | Extracted capacity and operation time with batteries of different ages.                                                                                                                         |          |

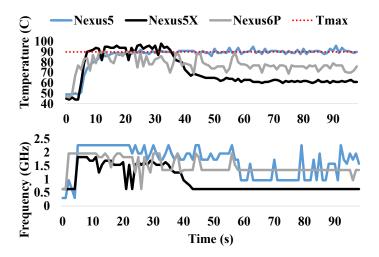

| 3.1          | Chip temperature and frequency traces from Nexus 5/5X/6P while                                                                                                                                  | 10       |

| J.1          | running Mibench benchmark                                                                                                                                                                       | 49       |

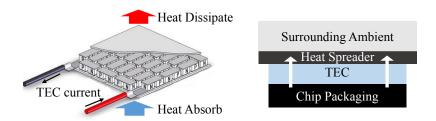

| 3.2          | TEC device and chip packaging with embedded TEC                                                                                                                                                 | 50       |

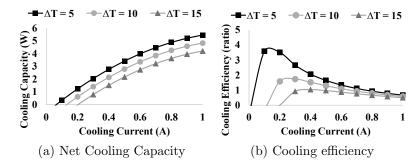

| 3.3          | (a) Net cooling capacity and (b) cooling efficiency of a TEC                                                                                                                                    |          |

| 0.0          | depending on the temperature difference between two sides                                                                                                                                       | 51       |

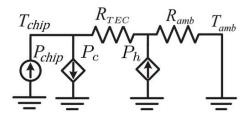

| 3.4          | Thermal circuit model of the TEC system                                                                                                                                                         | 53       |

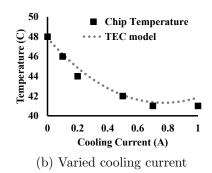

| 3.5          | Thermal model identification with various (a) processor frequencies                                                                                                                             |          |

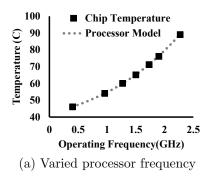

| 0.0          | and (b) TEC currents                                                                                                                                                                            | 54       |

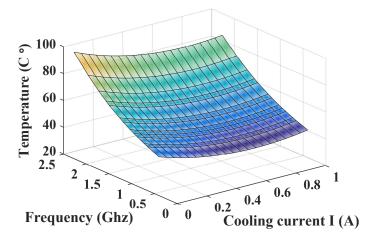

| 3.6          | Convexity of chip temperatures for the various processor frequencies                                                                                                                            | _        |

|              | and TEC cooling currents                                                                                                                                                                        | 56       |

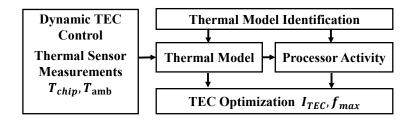

| 3.7          | Workflow diagram of dynamic TEC control                                                                                                                                                         | 57       |

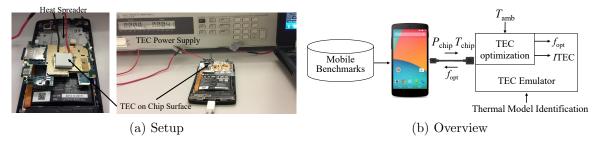

| 3.8          | Experiment and simulation setup.                                                                                                                                                                | 59       |

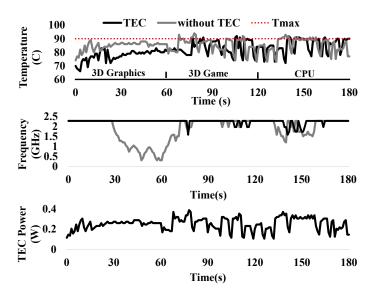

| 3.9          | Temperature, frequency, and cooling current traces from the experiment running the Antutu mobile benchmark                                                                                      | 60       |

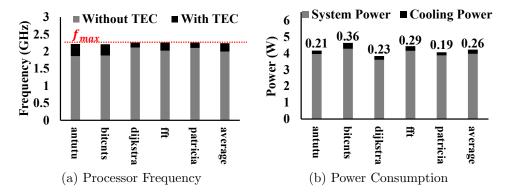

| 3.10         | (a) Processor frequency and (b) power consumption with and without the TEC for benchmark applications                                                                                           | 61       |

| 3.11         | (a) Processor frequency and (b) power consumption with and without the TEC for different ambient temperature                                                                                    | 62       |

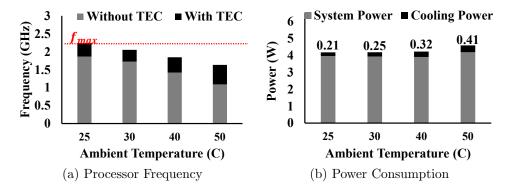

| 4.1          | Ambient temperature variations over time and the corresponding available computation power.                                                                                                     | 71       |

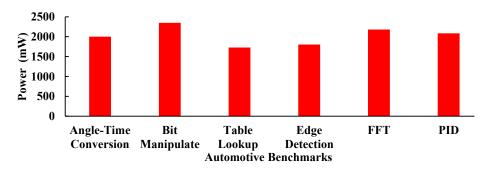

| 4.2          | Average power consumptions for various automotive applications                                                                                                                                  | 72       |

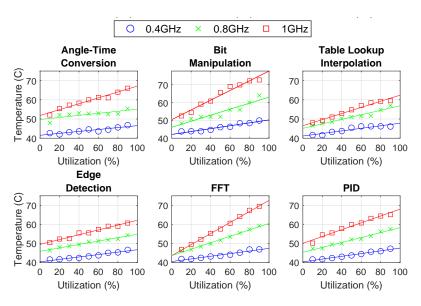

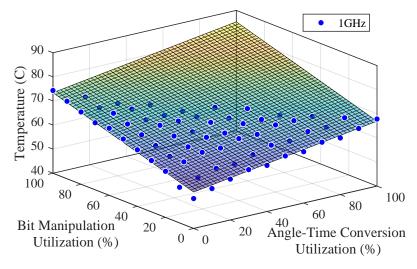

| 4.3          | Model validation with varying utilizations                                                                                                                                                      | 77       |

| 4.4          | Model validation with two periodic tasks (Bit manipulation, Angle-time Conversion)                                                                                                              | 77       |

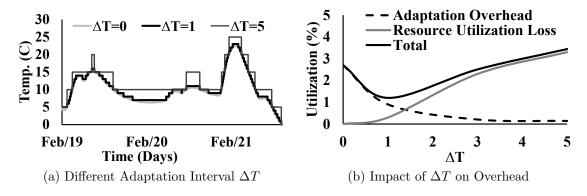

| 4.5          | Runtime adaptation with (a) different different adaptation intervals and (b) the trade-off between adaptation overhead and resource                                                             | •        |

| 4.6          | efficiency                                                                                                                                                                                      | 82       |

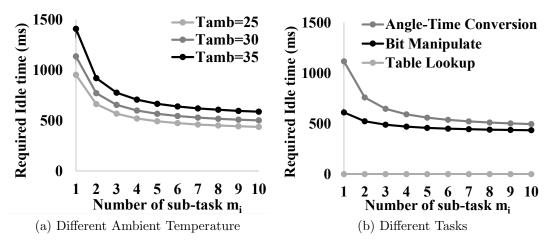

|              | different tasks decreases with the number of subtasks $m_i$                                                                                                                                     | 85       |

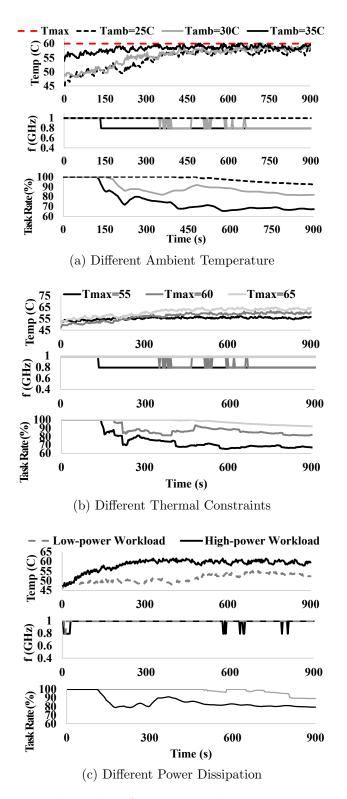

| 4.7          | Experimental results of RT-TRM showing the processor temperature, frequency, and task-rate traces under (a) different ambient temperatures, (b) thermal constraints and (c) power dissipations. | 90       |

|              |                                                                                                                                                                                                 |          |

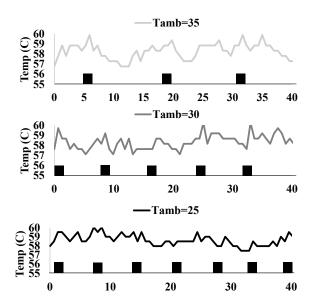

| 4.8  | Job schedule of a task (bit manipulation) and the corresponding      |     |

|------|----------------------------------------------------------------------|-----|

|      | temperature variation by RT-TRM                                      | 91  |

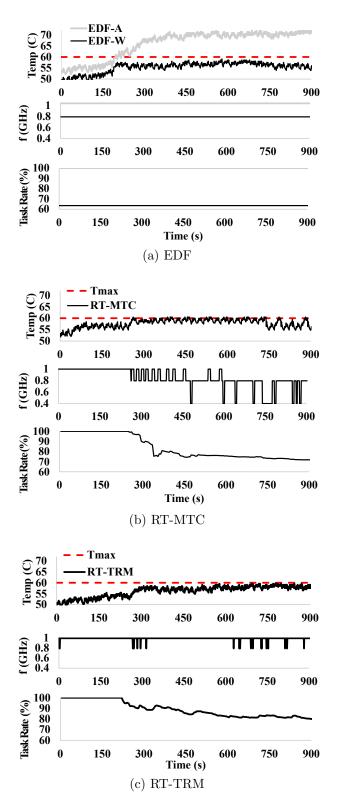

| 4.9  | Experimental results of different schemes showing the processor      |     |

|      | temperature, frequency, and task-rate traces.                        | 93  |

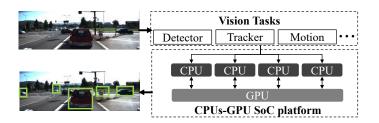

| 5.1  | Example of an embedded vision systems                                | 102 |

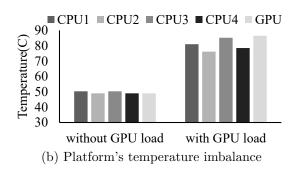

| 5.2  | CPUs surrounded by the GPU cluster on a SoC (Tegra X1), where        |     |

|      | the GPU's power dissipation affects the CPUs' temperatures, creating |     |

|      | temperature imbalance across the CPUs                                | 103 |

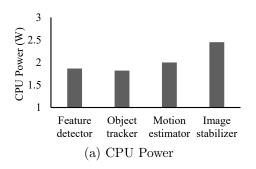

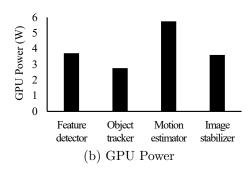

| 5.3  | Average power dissipations of (a) CPU and (b) GPU vary greatly by    |     |

|      | application tasks                                                    | 104 |

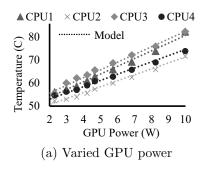

| 5.4  | (a) CPU temperatures resulting from varied GPU power dissipations    |     |

|      | and (b) maximum CPU temperature resulting from varied CPU and        |     |

|      | GPU power dissipations                                               | 111 |

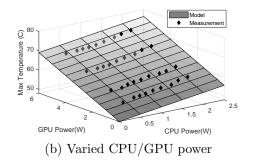

| 5.5  | Task-to-core assignment algorithms and their corresponding           |     |

|      | temperature increases                                                | 114 |

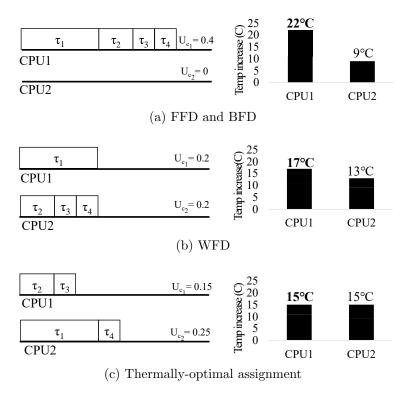

| 5.6  | RT-TAS avoids thermal throttling by reducing maximum                 |     |

|      | temperature, thus achieving a reliable response time                 | 126 |

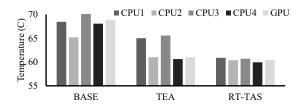

| 5.7  | Core-level peak temperature under different scheduling policies      | 127 |

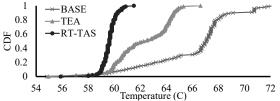

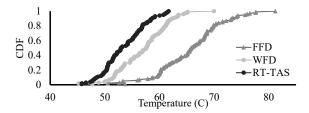

| 5.8  | Maximum temperature CDF under different scheduling policies          | 127 |

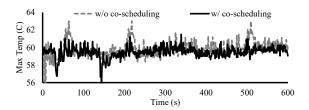

| 5.9  | Transient temperatures w/o and w/ CPU–GPU co-scheduling              | 128 |

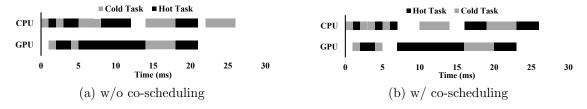

| 5.10 | Job schedule (a) w/o and (b) w/ co-scheduling                        | 128 |

| 5.11 | Maximum temperature CDF for different task sets                      | 130 |

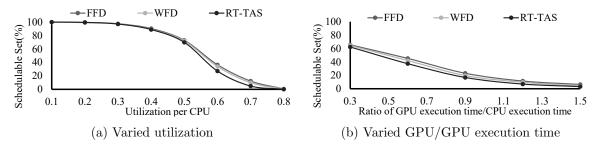

| 5.12 | Schedulability for various utilizations and GPU execution times      | 131 |

# LIST OF TABLES

| <u>Table</u> |                                                       |     |

|--------------|-------------------------------------------------------|-----|

| 1.1          | Selected state-of-the-art solutions                   | ŗ   |

| 1.2          | Summary of this thesis' contributions                 |     |

| 2.1          | Summary of the regression model                       |     |

| 3.1          |                                                       | 55  |

| 4.2          | Thermal parameters of the iMX6 processor              | 89  |

| 4.3          | WCET and min/maximum periods                          | 89  |

| 4.4          | The number of preemptions and idle-time per job       | 92  |

| 5.1          | Thermal coupling coefficients for the Tegra X1 (°C/W) | 11( |

| 5.3          | Task-set generation parameters                        | 129 |

#### ABSTRACT

While embedded systems such as smartphones and smart cars become essential parts of our lives, they face urgent thermal challenges. Extreme thermal conditions (i.e., both high and low temperatures) degrade system reliability, even risking safety; devices in the cold environments unexpectedly go offline, whereas extremely high device temperatures can cause device failures or battery explosions. These thermal limits become close to the norm because of ever-increasing chip power densities and application complexities. Embedded systems in the wild, however, lack adaptive and effective solutions to overcome such thermal challenges. An adaptive thermal management solution must cope with various runtime thermal scenarios under a changing ambient temperature. An effective solution requires the understanding of the dynamic thermal behaviors of underlying hardware and application workloads to ensure thermal and application quality-of-service (QoS) requirements. This thesis proposes a suite of adaptive and effective thermal management solutions to address different aspects of real-world thermal challenges faced by modern embedded systems.

First, we present BPM, a battery-aware power management framework for mobile devices to address the unexpected device shutoffs in cold environments. We develop BPM as a background service that characterizes and controls real-time battery behaviors to maintain operable conditions even in cold environments. We then propose eTEC, building on the thermoelectric cooling solution, which adaptively controls cooling and computational power to avoid mobile devices overheating. For the real-time embedded systems such as cars, we present RT-TRM, a thermal-aware

resource management framework that monitors changing ambient temperatures and allocates system resources to individual tasks. Next, we target in-vehicle vision systems running on CPUs-GPU system-on-chips and develop CPU-GPU co-scheduling to tackle thermal imbalance across CPUs caused by GPU heat. We evaluate all of these solutions using representative mobile/automotive platforms and workloads, demonstrating their effectiveness in meeting thermal and QoS requirements.

## CHAPTER I

# Introduction

Smartphones are becomeing essential to daily life; people use these devices not only to connect with others but also to navigate while driving, and even make mobile payments and conduct banking. Beyond the smartphone era, smart cars with advanced driver assistant systems (or even automated driving) are growing rapidly; both the European Union and United States have mandated that by 2020, all vehicles must be equipped with autonomous emergency-braking systems and forward-collision warning systems [34]. With the number of smartphones exceeding the world's population [49] and smart cars expected to hit 1.2 billion by 2025 [91], these embedded systems will further improve the quality and safety of life.

These and other smart applications/systems are enabled by (i) the increasing computational power of embedded systems and (ii) advances in artificial intelligence – a trend that will not slow with the rise of the edge computing paradigm, where interconnected smart/edge devices will perform major computations for end users [108]. Future embedded systems with advanced functionalities and increasing computational capabilities will soon be integrated into every aspect of life, rendering them indispensable.

Such embedded systems, however, face urgent thermal challenges in both extreme thermal conditions (i.e., high and low temperatures) where their reliability is compromised, such as in the following cases:

- Device overheating shortens the lifetime of a device and severely degrades its reliability, even risking safety (e.g., vehicle breakdowns or smartphone explosion).

- Extremely low-temperatures cause unpredictable shutoffs of battery-powered devices; for example, devices might shut off even when their batteries are shown to have 20% remaining capacity.

Such systems must cope with changing environmental temperature to overcome these thermal challenges. Dynamic thermal behaviors of application workloads and underlying platforms must also be accounted to meet the thermal requirements. This thesis identifies the new thermal challenges in modern embedded systems (§1.1), highlights dynamic thermal characteristics therein (§1.2) along with state-of-the-art (§1.3), and proposes a set of thermal management solutions to address those deficiencies (§1.4).

# 1.1 Thermal Challenges

As embedded systems evolve, thermal limits are close to the norm where system reliability is compromised, as is evident in Fig. 1.1.

### 1.1.1 High Temperature

Dangerously high temperatures severely degrade a system's reliability, and even risk safety. Device overheating often makes the system unavailable (Fig. 1.1a) and can cause battery explosion (Fig. 1.1b), such as in the example of Samsung Note 7 explosions [93]. These thermal emergencies not only cause monetary loss but can also lead to catastrophic consequences for driving, medical and wearable applications. When a given temperature threshold is reached, these devices are often

(a) Device Unavailable

(b) Battery Explosion

(c) Unexpected Device Shutoff

Figure 1.1: Thermal challenges in embedded systems threatening system reliability and user's safety.

cooled by stopping/slowing their operations, and these applications therein experience significant lagging and quality-of-service (QoS) degradation.

#### 1.1.2 Low Temperature

Cold environments also limit the availability of battery-powered embedded systems (Fig. 1.1c). This is because the power-supply capability of batteries severely degrades in low temperatures. Devices unpredictably shut off even when the battery is shown to have plenty of capacity remaining, and such unmanageable device shutoffs may lead to disastrous situations for mission-critical applications. In 2017, Apple attempted to avoid such premature/unexpected device shutoffs. They limited the maximum allowed discharge current (through regulating the maximum speed of the processors) on iPhones in cold environments. This solution, however, caused noticeable degradation in the QoS perceived by device users, leading to multiple lawsuits against Apple [92].

Furthermore, these thermal challenges will become worse with increasing application complexities [47] and chip-power densities but a fixed thermal limit [110]. Simultaneously, as people's lives increasingly rely on these devices, their thermal reliability will become even more significant.

# 1.2 Dynamic Thermal Behaviors

Thermal behaviors of embedded systems are often dynamic, making their thermal management challenging. Three major dynamic factors dictate device temperature: ambient temperature, hardware thermal characteristics and dynamic application behaviors.

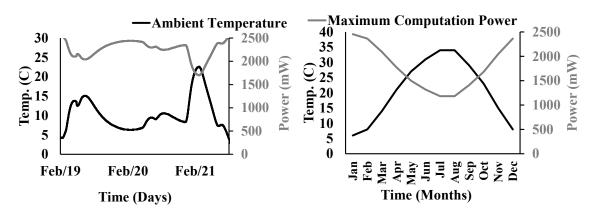

## 1.2.1 Changing Ambient Temperature

Embedded systems, unlike desktops or data-centers, experience a wide range of environmental variations especially ambient temperature during their operation/life. Ambient temperature changes dynamically, and their seasonal and locational variations are very wide. Because a device's temperature depends on the ambient temperature, changing ambient temperature under a fixed thermal limit indicates a changing thermal budget.

#### 1.2.2 Hardware Thermal Variabilities

Other issues pertaining to thermal management are the unique thermal characteristics of underlying hardware components. To manage the thermal behaviors of computing platforms, cooling devices must be captured to manage system temperatures effectively. To enable reliable system operation, the temperature-dependent characteristics of batteries must also be captured, which are the dominant power-supply hardware in embedded systems.

#### 1.2.3 Dynamic Application Workloads

Finally, application workloads fluctuate widely, causing high temperature fluctuations and peak temperatures. In embedded systems, workloads in response to sporadic user activities exhibit a bursty pattern for user-interactive applications. Different application contexts (e.g., driving contexts such as highway/urban driving

Table 1.1: Selected state-of-the-art solutions.

| System                    | Ambient<br>Temperature | Hardware<br>Variabilities | Dynamic<br>Workloads | Deployment |

|---------------------------|------------------------|---------------------------|----------------------|------------|

| [26, 30, 31, 51, 77, 119] | -                      | -                         | -                    | Simulation |

| [13, 68, 70, 78, 127]     | -                      | -                         | $\checkmark$         | Simulation |

| [43, 63, 99, 107, 112]    | -                      | $\checkmark$              | -                    | OS change  |

| [28, 54, 55, 87]          | $\checkmark$           | -                         | -                    | Simulation |

or parking) also create large variations in workloads. Such dynamic workloads must be captured to effectively predict/regulate peak temperatures, thereby meeting thermal requirements.

## 1.3 State of the Art

Extensive studies have been conducted on thermal management [76] at both the hardware- (e.g., architecture design, floorplan, and hardware throttling) and software-level (e.g., task assignment, scheduling, and idle insertion). Thermal-aware dynamic voltage/frequency scaling (DVFS) and task scheduling have been active subjects of research attempting to meet timing and thermal constraints. DVFS scheduling determines the voltage and frequency of a processor to minimize power consumption [15, 129] and the peak temperature subject to timing constraints on single-core [30, 31, 119] or multi-core platforms [26, 51]. These solutions, however, do not deal with the problems of a changing environment, hardware thermal variabilities, and dynamic application workloads.

To address the thermal impact of dynamic workload, researchers have focused on different task-level power dissipations to reduce the peak temperature [13,70] or maximize throughput [68, 127] through interleaving the execution of hot and cold tasks. Through analyzing such task-level power variations, the peak temperature was derived to meet the thermal constraint [13,78].

To capture unique thermal characteristics/variabilities of the underlying

hardware, researchers have analyzed a platform's temperature imbalance across CPUs [79] and CPUs-GPU [96, 107] platforms. CPUs-GPU thermal coupling is known to limit a core's maximum frequency, which is greatly affected by the GPU's heat dissipation [96,99]. Maestro [107] focused on characterizing a thermally efficient core to control the frequency in heterogeneous systems. The infrared imaging was used to characterize the CPUs-GPU thermal coupling, demonstrating thermal challenges in an integrated CPU and GPU [43]. Singla et al. [112] proposed a thermal modeling methodology through system identification for a heterogeneous mobile platform. A few researchers have considered battery characteristics from the system perspective. Xie et al. analyzed thermal coupling in smartphones between the system and battery [120]. B-MODS [63] used battery-aware intermittent discharge patterns on mobile devices to exploit the battery relaxation effect.

Several researchers have considered dynamic environments and developed adaptive thermal management to meet both thermal and QoS requirements. Feedback controller approaches were proposed to regulate the processor temperature by adjusting the processor utilization [54] or operating frequency [55] subject to timing constraints. Furthermore, a few online scheduling algorithms have been proposed to enhance the thermal reliability of homogeneous [28, 87] and heterogeneous [86] multiprocessor platforms.

Unfortunately, state-of-the-art solutions fall short in adaptively managing dynamic thermal behaviors, providing a deployable solution and/or satisfying both QoS and thermal requirements. Many of the existing approaches, however, have been evaluated using thermal simulations but have neither been implemented nor tested with realistic platforms and workloads.

Table 1.2: Summary of this thesis' contributions.

| System          | Target System | Ambient<br>Temperature | Hardware<br>Variabilities | Dynamic<br>Workloads | Deployment                          |

|-----------------|---------------|------------------------|---------------------------|----------------------|-------------------------------------|

| BPM [1]         | Mobile        | ✓                      | ✓                         | ✓                    | User-level service                  |

| <b>eTEC</b> [2] | Mobile        | $\checkmark$           | $\checkmark$              | $\checkmark$         | User-level service + cooling device |

| RT-TRM [3]      | Automotive    | $\checkmark$           | -                         | $\checkmark$         | User-level service $+$ OS change    |

| RT-TAS $[4]$    | Automotive    | -                      | $\checkmark$              | $\checkmark$         | User-level APIs                     |

## 1.4 Thesis Statement and Contributions

Although existing research work considered thermal challenges, embedded systems in the wild still lack effective and adaptive solutions to cope with extreme thermal conditions. An effective thermal management solution requires understanding the dynamic thermal behaviors of application workloads and the underlying hardware to ensure thermal and application QoS requirements, and moreover, an adaptive one must cope with various runtime thermal scenarios under the changing ambient temperature.

Thesis Statement: The thermal management systems for embedded applications developed in this thesis meet both thermal and QoS requirements under (i) changing ambient temperature, (ii) platform thermal variabilities and (iii) dynamic application workloads.

In this thesis, we improve on the state of the art by proposing a set of effective and adaptive thermal management systems span various environment and applications (Table 1.2) that target mobile devices: BPM and eTEC; and automotive systems: RT-TRM and RT-TAS. Each of these thermal management systems advances the state of the art in dynamic thermal management by addressing different aspects of dynamic thermal behaviors. These thermal management systems meet thermal and QoS requirements, and thus provide a practical and deployable solution.

#### 1.4.1 BPM

Many users have reported experiencing unexpected shutoffs of their mobile devices, such as smartphones and tablets, even when the device battery is shown to have >30% remaining capacity. After examining the problem from both the user and device sides, we have discovered the cause of such unexpected shutoffs to be the large and dynamic voltage drop across the device battery's internal impedance, which, in turn, is caused by the dynamics of mobile devices' power supply and demand: (i) a battery's dynamic internal impedance, which varies with the state-of-charge (SoC), temperature, and age, together with the device's bursty discharge current, cause a voltage drop across the battery's impedance to fluctuate; (ii) this drop reduces the voltage supplied to the device, and if the reduction is too large, this shuts off the device even before the battery is fully drained.

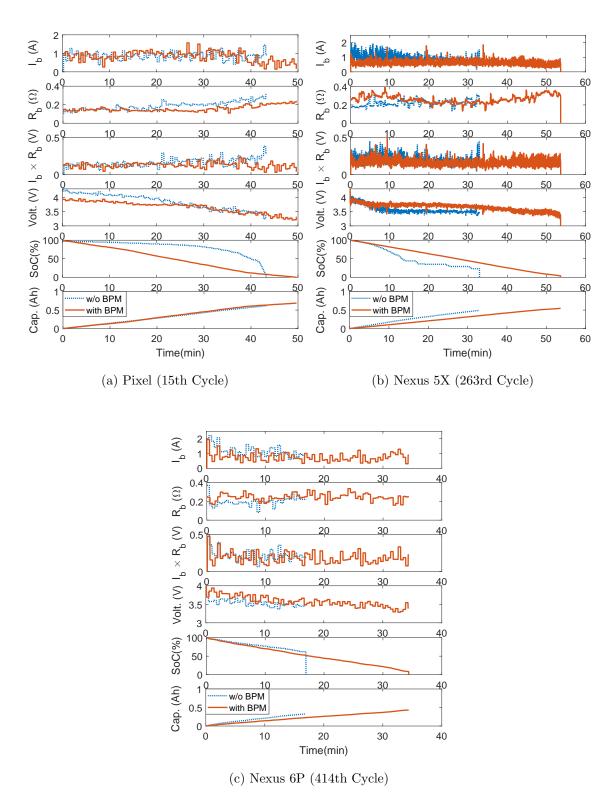

To fix such unexpected shutoffs, we designed a novel battery-aware power management (BPM) middleware for mobile devices. This middleware accounts for the dual-dynamics of device operation — capturing the dynamic battery impedance and adaptively controlling the device's dynamic runtime discharge current — thereby regulating the battery's voltage drop and achieving reliable and extended device operation. Specifically, BPM profiles the battery impedance at different SoCs and temperatures using a novel duty-cycled charging method, and then regulates, at runtime, the discharge current based on the thus-constructed battery profile. We implemented and evaluated BPM on four commodity smartphones from different original equipment manufacturers (OEMs), demonstrating that BPM prevents unexpected device shutoffs and extends the device operation time by 1.16–2.03×.

#### 1.4.2 eTEC

In this project, we investigated device overheating, where underlying processors were throttled to cool devices, causing mobile apps to suffer significant degradation

in performance. Fans or heat sinks are not a viable option for mobile devices, which calls for a new portable cooling solution. Thermoelectric coolers (TECs) are scalable and controllable cooling devices that can be embedded into mobile devices on the chip surface. This project presents a thermoelectric cooling solution that enables efficient thermal management of processors in mobile devices. Our goal was to minimize performance loss from thermal throttling by efficiently using thermoelectric cooling. Because mobile devices experience large variations in workload and ambient temperature, our solution adaptively controls cooling power at runtime. Our evaluation on a smartphone using mobile benchmarks demonstrated that the performance loss from the maximum speed was only 1.8% with a TEC compared to 19.2% without the TEC.

#### 1.4.3 RT-TRM

Whereas BPM and eTEC focus on mobile devices, we subsequently focused on embedded real-time applications such as automotive systems. For real-time automotive systems, we demonstrated the importance of accounting for dynamic ambient temperature and task-level power dissipation in resource management to meet both thermal and timing constraints. To address this problem, we proposed a real-time thermal-aware resource management (RT-TRM) framework. We first introduced a task-level dynamic power model that could capture different power dissipations with a simple task-level parameter called the activity factor. We then developed two new mechanisms, adaptive parameter assignment and online idle-time scheduling. The former adjusts voltage/frequency levels and task periods according to the varying ambient temperatures while preserving feasibility. The latter generates a schedule by allocating idle times efficiently without missing any task or job deadlines. By tightly integrating the solutions of these two mechanisms, we could guarantee both thermal and timing constraints in the presence of dynamic ambient

temperature variations. We implemented RT-TRM on an automotive microcontroller to demonstrate its effectiveness, improving resource utilization by 18.2% over other runtime approaches while simultaneously meeting both thermal and timing constraints.

#### 1.4.4 RT-TAS

Because modern cars perform real-time vision processing using high-performance CPUs-GPU system-on-chip (SoC), they face greater thermal problems than before, which in turn cause higher failure rates and cooling costs. We used a representative vision platform to demonstrate the importance of scheduling the CPU and GPU while accounting for their thermal coupling, which incurred significant temperature imbalance on the platform. To address this problem, we proposed RT-TAS, a real-time thermal-aware CPUs-GPU scheduling framework. We first developed a CPUs-GPU thermal coupling model that could capture the different CPU temperatures caused by GPU power dissipation. We then used the model for thermally-balanced task-to-core assignment and CPU-GPU co-scheduling. The former addresses the platform's temperature imbalance by assigning tasks efficiently to cores while preserving scheduling feasibility. The latter, building on the thermally-balanced assignment, co-schedules the CPU and GPU to mitigate peak total power dissipation without missing any task deadlines. We implemented and evaluated RT-TAS on a representative automotive vision platform to demonstrate its effectiveness, achieving a 1.52× improvement in platform lifetime or savings on cooling cost of US\$ 16.4 over other approaches by reducing the maximum temperature while meeting timing constraints.

## CHAPTER II

**BPM: Battery-Aware Power Management**

### 2.1 Introduction

Many users are reported to have suffered the unexpected shutoffs of their mobile devices — even when the device batteries are shown to have >30% remaining capacity — on both Android [66] and iOS platforms [115], especially in cold environments. These unexpected shutoffs prevent users from making and receiving important calls and texts even when the device batteries have sufficient remaining capacity. Apple introduced an update to iOS 10.2.1 to remedy the unexpected shutoff of iPhones with aged batteries. This update, however, (i) did not fully address the underlying issue [115], and (ii) slowed the phone noticeably [6], leading to multiple lawsuits against Apple [92].

Causes: Large and Dynamic Internal Voltage Drop. Our experiments showed the cause of such unexpected device shutoffs to be a large voltage drop across the battery's internal impedance, causing an insufficient voltage supplied to the device<sup>1</sup>, and thus shutting off the device.<sup>2</sup> The internal voltage drop is determined by the battery's impedance and the device's discharge current, both of which vary

<sup>&</sup>lt;sup>1</sup>Mobile devices require a minimum voltage (e.g.,  $V_{\rm bat}>3.4{\rm V}$ ) to operate.

<sup>&</sup>lt;sup>2</sup>Mobile devices may shut off when their batteries/chips are overheated. These shutoffs, however, are intentionally-triggered (for safety) and well-tracked by both Android and iOS, and are thus not considered "unexpected".

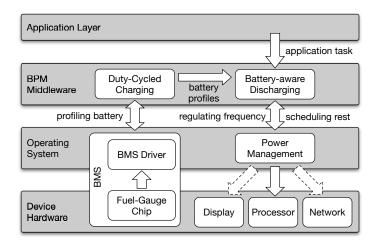

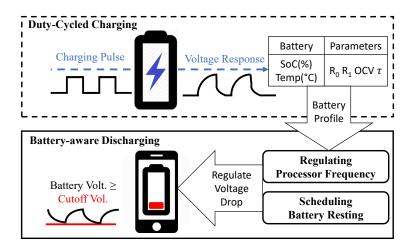

Figure 2.1: Battery-aware power management middleware.

over device operation: (i) the battery's impedance varies with the state-of-charge (SoC)<sup>3</sup> and rises as the battery ages or temperature falls [62], and (ii) a mobile device's discharge current is often bursty in response to user activities [102]. Such "dual-dynamics" of battery impedance and discharge current magnify the uncertainty of the battery's internal voltage drop, making it difficult to predict/regulate the battery's voltage output. Notably, the dependency of a battery's impedance on its age or the environmental temperature exacerbates the unexpected shutoffs as it ages or when it operates in a cold environment (§2.3).

Fixes: Battery-Aware Power Management (BPM). To mitigate unexpected device shutoffs, we present a novel BPMmiddleware that is compatible with commodity mobile devices and require no additional hardware — except for a typical charger — or OS modifications. BPM captures the dynamic battery impedance at different SoCs and temperatures, updates it as the battery ages, and regulates the device's runtime discharge current to ensure a sufficient voltage supply to operate the device whenever possible, thereby achieving a reliable and extended device operation. Thus, users can use their phones for longer and in a more predictable manner (§2.4.1). Specifically, BPM fixes unexpected device shutoffs with the joint management of battery charging and

<sup>&</sup>lt;sup>3</sup>SoC is the percentage of remaining capacity relative to the total usable capacity when the battery is fully charged.

discharging via close interactions with the (lower) OS layer and (upper) application layer (see Fig. 2.1):

- Duty-Cycled Charging. BPM becomes aware of the device battery by profiling (and updating) the battery impedance at different SoC levels with novel duty-cycled charging: the battery is rested after being charged to a set of discretized SoC levels, and the battery is characterized at a specific SoC level based on the battery voltage during the corresponding rest period. BPM further compensates the temperature-dependency of the thus-profiled battery impedance according to the environmental temperature. This duty-cycled charging, however, requires more time to fully charge the battery. To ensure no perceivable degradation of user experience caused by the prolonged charging, BPM applies the duty-cycled charging only when the device is charging overnight (as mobile device users commonly do), and furthermore, it allows a sufficient time to fully charge/characterize the battery [64] (§2.4.2).

- Battery-Aware Discharging. BPM adaptively regulates the device's operation, and hence battery discharging, based on this battery-awareness. Specifically, BPM (i) estimates the battery impedance based on the above-captured impedance—SoC relationship; (ii) identifies the maximum allowed discharge current; (iii) regulates the device's discharge current below the allowed maximum by limiting the maximum processor frequency; and then (iv) schedules rest periods between consecutive device operations to restore the battery voltage before executing the next operation. BPM uses the processor frequency and scheduling as control knobs to regulate the discharge current, instead of the operation of other device modules, such as display and networking (see Fig. 2.1). This was based on our empirical observation that the major dynamics of a device's discharge current are attributed to the processor (§2.4.3). Moreover, BPM limits the maximum processor frequency

only to the necessary degree, thereby minimizing degradation in user-perceived experience. Our experiments showed that BPM prevented unexpected device shutoffs at a cost of only a 1.1% reduction in processor frequency, whereas the iOS 10.2.1 update reduces the processor frequency by 9.1% according to the empirical measurements in [6].

We implemented and evaluated BPM on the following smartphones: two Nexus 5X, one Nexus 6P, and one Pixel (§2.5). Our experimental results demonstrated BPM to (i) prevent unexpected device shutoffs, and (ii) extend device operation by 1.16–2.03× compared with the default battery saver mode of these devices.

**Contribution:** This chapter makes the following main contributions:

- Demonstrations of the root causes of unexpected mobile device shutoffs and the importance of accounting for devices' dynamic power supply and demand together to avoid unexpected shutoffs.

- Design of BPM, a novel battery-aware power management middleware that fixes unexpected device shutoffs and extends device operation (§2.4).

- Implementation (§2.5) and evaluation of BPM on four commodity mobile devices from different OEMs (§2.6).

# 2.2 Background

Presented in the following subsection is the necessary background information of mobile device batteries and their management.

#### 2.2.1 Mobile Devices and Their Batteries

Batteries are used to power the hardware components of a mobile device, such as processors, displays, and communication modules, with the typical architecture

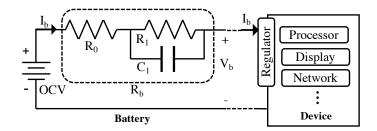

Figure 2.2: Equivalent circuit model of a mobile device: the device will shut off when the battery voltage  $V_b$  is lower than the minimum level required by the device.

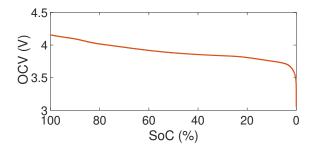

Figure 2.3: The OCV-SoC relationship of batteries.

illustrated in Fig. 2.2. The device battery is abstracted by an equivalent circuit model (the left part of Fig. 2.2) consisting of [123]:

- 1. An ideal voltage source, providing the battery's open-circuit voltage (OCV), defined as the voltage between its terminals without loads/charger connected. A battery's OCV has a monotonic relationship with the battery's remaining capacity (see Fig. 2.3, which presents the example of the battery of a Nexus 5X), which is the basis for SoC estimation commodity mobile devices [59].

- 2. A resistor-capacitor network (i.e.,  $R_0$ ,  $R_1$ ,  $C_1$ ), which we call the battery's internal impedance  $R_b$ .

When the battery discharges current  $I_b$ , the serial resistance  $R_0$  causes an instant voltage drop

$$\Delta V_{inst.} = I_b \cdot R_0. \tag{2.1}$$

The parallel connection of  $R_1$  and  $C_1$  further triggers a gradual voltage drop of

$$\Delta V_{trans.}(t) = I_b \cdot R_1 - R_1 \cdot C_1 \frac{dV_b(t)}{dt}, \qquad (2.2)$$

which converges (i.e., when  $\frac{dV_b(t)}{dt} = 0$ ) at

$$\Delta V_{trans.} = I_b \cdot R_1. \tag{2.3}$$

A combination of Eqs. (2.1) and (2.2) shows that the battery's output voltage  $V_b(t)$  can be described as

$$V_b(t) = OCV(SoC) - \Delta V_{inst.} - \Delta V_{trans.}(t)$$

$$= OCV(SoC) - (R_0 + R_1) \cdot I_b + R_1 \cdot C_1 \cdot \frac{dV_b(t)}{dt}. \tag{2.4}$$

Note that by defining the discharge/charge current as positive/negative values, Eqs. (2.1)–(2.4) hold for charging devices as well.

The mobile device on the right of Fig. 2.2 requires the minimum input voltage  $V_b^{cutff}$  to operate (e.g., 3.3–3.4V for mobile phones [63]), otherwise the device will shut off. This cutoff voltage — usually implemented using voltage regulators [62] — ensures a sufficient voltage to power hardware components and avoids the deep discharging of the battery, which accelerates battery degradation.

# 2.2.2 Battery Management of Mobile Devices

The battery management system (BMS) of commodity mobile devices consists of a fuel-gauge chip and the BMS driver/firmware in the OS (see Fig. 2.1). The fuel-gauge chip monitors the battery information in real time, such as the voltage, current, and temperature. The BMS driver/firmware then estimates advanced battery information such as SoC and battery health using this raw information [17]. The OS displays

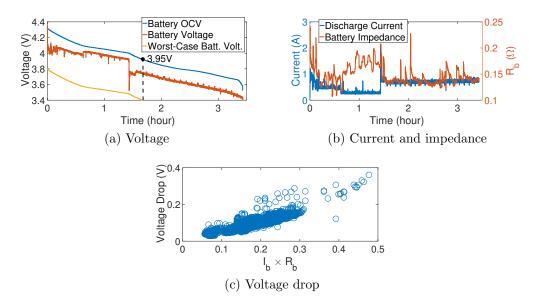

Figure 2.4: Operating a Nexus 5X phone: playing a video, idling, and then playing a game until shutoff.

this battery information to users and takes coarse-grained actions (e.g., enabling the battery saver mode or disabling the camera) when the battery's remaining capacity is low. The OS also maintains device/battery usage statistics to calculate the power usage of each app or device module, and uses them to adjust the processor frequency through dynamic voltage frequency scaling (DVFS).

# 2.3 Causes of Unexpected Device Shutoffs

With the understanding of the power architecture of mobile devices, this section analyzes and validates the causes of unexpected device shutoffs.

**Device Operation and Shutoff.** We first use the empirical traces shown in Fig. 2.4 to illustrate how mobile devices operate,<sup>4</sup> from which we make the following three key observations.

O1. The battery voltage decreases during the phone's operation until it reaches

<sup>&</sup>lt;sup>4</sup>These traces were collected with a Nexus 5X phone in a room temperature, during which the phone was used to play a Youtube video (i.e., the first 38 minutes), kept idle (i.e., 38–86 minutes), and then play a game until shutoff (i.e., 86–206 minutes).

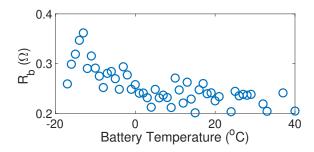

Figure 2.5: Battery impedance rises as temperature falls.

approximately 3.4V, at which point the phone shuts off, as shown in Fig. 2.4(a).

- **O2.** Both the discharge current and battery impedance vary during device operation (see Fig. 2.4(b)).

- O3. The internal voltage drop of the battery that is the difference between the "Battery OCV" and "Battery Voltage" in Fig. 2.4(a) depends on both the discharge current and impedance. This can be observed in Fig. 2.4(c), where the voltage drop (i.e., y-axis) and the term  $I_b \cdot R_b$  (i.e., x-axis) are calculated from Fig. 2.4(a) and (b), respectively. This can also be derived from Eq. (2.4): the battery's output voltage  $V_b$  is determined by its internal resistance and capacitance (i.e.,  $R_0$ ,  $R_1$  and  $C_1$ ) and discharge current  $I_b$ . Note the markers in Fig. 2.4(c) are below the line of y = x because of the insufficient time for the battery voltage to be stabilized during this measurement (i.e.,  $dV_b(t)/dt > 0$  in Eq. (2.2)) the collected voltage drop has not yet reached its maximum.

These observations led to our conjecture that a large voltage drop over a battery's internal impedance may reduce the battery voltage too much to power the device, thereby causing unexpected device shutoffs. This large voltage drop is likely to occur in practice because of a dynamically changing battery impedance and discharge current, especially in view of the fact that the battery impedance also varies with temperature  $T_b$ ; that is, the impedance rises as the temperature falls, as shown in Fig. 2.5 with the Nexus 5X.

Assuming this conjecture holds, the "Worst-Case Battery Voltage" in Fig. 2.4(a) plots the lower-bound of the battery voltage, meaning the lowest possible voltage without shutting the device off. This is derived using

$$V_{\text{worst}} = OCV(SoC) - \max\{I_b\} \cdot \max\{R_b\},\tag{2.5}$$

where  $\max\{I_b\}$  and  $\max\{R_b\}$  are extracted from Fig. 2.4(b), showing that the phone may shut off with an OCV as high as 3.95V, which maps to (according to Fig. 2.3) an SoC of nearly 70%.

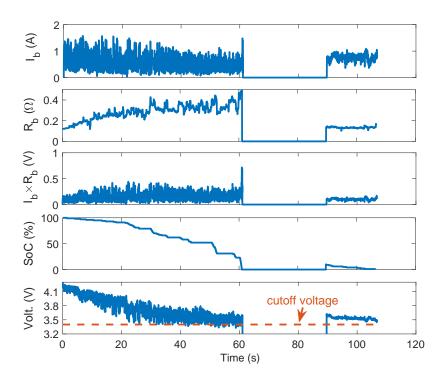

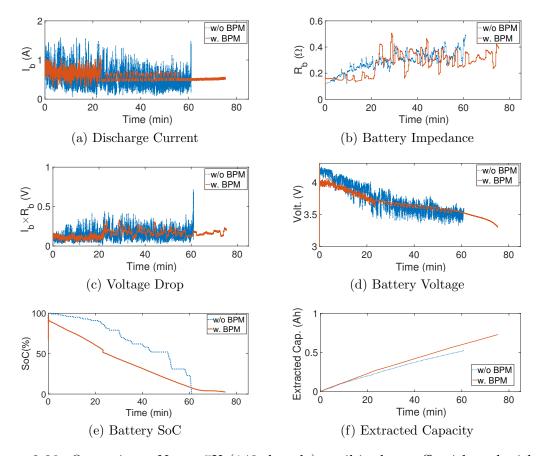

Case Studies of Unexpected Shutoffs. To corroborate this conjecture, we conducted case studies to trigger unexpected shutoffs of a Nexus 5X phone by magnifying the voltage drop across its battery's impedance (i.e.,  $I_b \cdot R_b$ ). Specifically, we operated a fully-charged Nexus 5X phone in a freezer ( $-5^{\circ}$ C) with the User Interaction (UI) exerciser [8] on until it shut off (thus with increasing  $R_b$  and  $I_b \cdot R_b$ ), warmed it in room temperature (thus  $R_b$  and  $I_b \cdot R_b$  decreased), and then attempt to turn it on and operate it further without charging. Fig. 2.6 plots the discharge current, battery impedance, voltage drop, and battery voltage supplied to the phone during this measurement, showing that,

- the discharge current was highly dynamic/bursty;

- the battery's internal impedance rose as the temperature fell;

- the phone shut off when the voltage dropped to approximately 3.4V, but then it was successfully turned back on after being warmed in room temperature delivering another 330mAh capacity or operating for an additional 18 minutes without having its battery charged. The battery's voltage drop before the unexpected shutoff was 0.49V, which reduced to 0.14V after being warmed in room temperature (e.g., at the 88th minute) and thus we were able to turn the

Figure 2.6: Unexpected shutoff of a Nexus 5X smartphone in a cold ambient temperature.

phone on again.

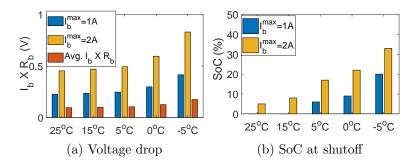

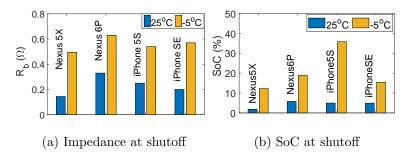

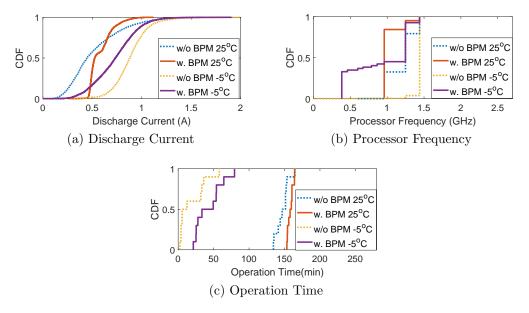

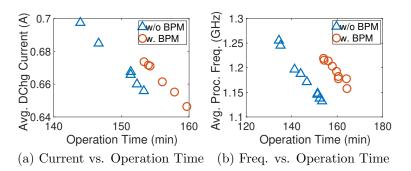

Next, we repeated the experiments while varying the ambient temperature from -5 to  $25^{\circ}$ C and the maximum discharge current from 1 to 2A. The results are plotted in Fig. 2.7, and show that (i) unexpected shutoffs were observed at all explored temperatures, and (ii) the voltage drop increased and the phone shut off with up to 33% SoC when discharging with a large current in cold ambient temperatures. We have conducted similar experiments with a Nexus 6P and iPhone 5S and SE<sup>5</sup> and made similar observations, as summarized in Fig. 2.8. Note the iPhone SE had the iOS 10.2.1 update to prevent unexpected shutoffs, whereas the iPhone 5S did not. Although this update reduced the unexpected shutoffs at  $-5^{\circ}$ C (i.e., from 35% SoC on iPhone 5S to 15% SoC on iPhone SE), the problem still persisted. More importantly, the update degraded the phone performance significantly, for example, it reduced the

$<sup>^5</sup>$ All these devices are within their battery warranty (e.g., 500 complete charge/discharge cycles).

Figure 2.7: Voltage drop at shutoff vs. the average voltage drop and SoC at shutoff of a Nexus 5X battery.

Figure 2.8: Battery impedance and SoC when different mobile devices shut off.

average processor frequency by 9.1% [6].

These case studies confirmed our conjecture that a large voltage drop across the battery's internal impedance (i.e.,  $I_b \cdot R_b$ ) causes unexpected device shutoffs, which are prevalent across Android and iOS devices.

# 2.4 Fixes for Unexpected Device Shutoffs

These causes of unexpected device shutoffs also inspire their remedy, i.e., regulating the voltage drop across battery impedance  $I_b \cdot R_b$ , where both  $I_b$  and  $R_b$  vary.

#### 2.4.1 Overview

As mobile devices have little control over their battery's internal impedance  $R_b$ , BPM regulates  $I_b \cdot R_b$  by actively limiting  $I_b$  based on the real-time estimation of  $R_b$ .

Figure 2.9: BPM profiles the device battery during charging and regulates the voltage drop during discharging.

Specifically, BPM uses (i) duty-cycled charging management to profile the dynamic battery characteristics thereby facilitating the real-time estimation of  $R_b$ , and (ii) battery-aware discharging management to regulate the device's discharge current  $I_b$  at runtime (see Fig. 2.9). During battery charging (dotted line), BPM charges the device with a duty-cycled current followed by a rest period, and then determines the battery parameters — i.e.,  $\langle OCV, R_0, R_1, C_1 \rangle$  — at each SoC based on the voltage observed during the rest period. At runtime, BPM further compensates these battery parameters based on the environmental temperature using a temperature dependency model (§2.4.2). During discharging (solid line), BPM (i) estimates the runtime battery impedance, (ii) identifies in real time the maximum allowed discharge current based on battery impedance, (iii) determines the thus-allowed maximum processor frequency, and (iv) allocates a rest period between operations to restore the battery voltage — using the recovery effect of batteries [63] — before executing the next operation (§2.4.3).

Note that the BPM middleware implements the duty-cycled charging and discharging management by leveraging readily available BMS and the DVFS drivers of commodity mobile devices, and thus requires no special hardware — except a

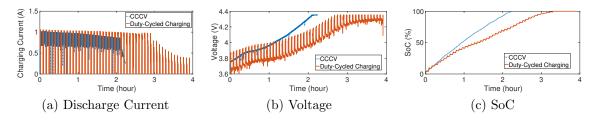

Figure 2.10: BPM's duty-cycled charging vs. standard CCCV charging.

typical charger — or OS modifications (§2.5).

## 2.4.2 Profiling Batteries During Charging

BPM profiles the battery's parameters as functions of battery SoC and temperature, and then stores them as lookup tables.

Duty-Cycled Charging. BPM constructs and updates these lookup tables by charging the devices with a customized duty-cycle: in each cycle, the battery is charged with a current  $I_c$  for a duration of  $t_c$ , and then it is rested the battery for a duration of  $t_r$ . BPM implements this duty-cycled charging by enabling/disabling the device's charging,<sup>6</sup> which also simplifies BPM because the charging current  $I_c$  will automatically be determined by the device's charging chip — BPM only needs to control  $t_c$  and  $t_r$ . Note that when the device's charging is disabled with the charger connected, the device's operation will be powered by the charger, thereby resting the battery.

Fig. 2.10 depicts the duty-cycled charging current, battery voltage, and SoC during BPM's charging of a Nexus 5X phone, and compares them with constant-current constant-voltage (CCCV) charging, which is commonly used in mobile devices [64]. Clearly, BPM's duty-cycled charging prolongs the time required to fully charge the battery, for example, Fig. 2.10 shows that BPM requires approximately 1.4 hours longer to fully charge the battery compared with CCCV. To preserve the user-perceived QoS,

$<sup>^6</sup>$ This charging control can be achieved, e.g., by configuring  $/sys/class/power\_supply/bms/battery\_charging\_enable$  in Android devices.

BPM applies duty-cycled charging only when mobile devices are charged overnight, which provides sufficient time to fully charge the battery and is very common for most mobile device users [64]. Moreover, resting the battery after each charging cycle slows battery aging [59].

In addition, note that BPM's duty-cycled charging differs from existing pulsed charging; that is, BPM exploits the rest periods to profile the battery, as we explain next.

Battery Voltage During Resting. BPM uses the battery voltage during rest periods to estimate battery parameters at specific SoC levels. According to Eqs. (2.1)–(2.4), resting battery at time 0 after charging it with current  $I_c$  yields:

$$V_b(0^-) = OCV - I_c \cdot (R_0 + R_1), \tag{2.6}$$

$$V_b(0^+) = OCV - I_c \cdot R_1,$$

(2.7)

$$V_b(t) = OCV - I_c \cdot R_1 \cdot e^{-\frac{t}{R_1 \cdot C_1}} \qquad (t > 0),$$

(2.8)

showing the battery voltage to (i) drop instantly by  $\Delta V_{inst.} = I_c \cdot R_0$  because of the ohmic voltage drop across  $R_0$  (i.e., Eq. (2.6) to Eq. (2.7)), and (ii) drop gradually afterwards according to Eq. (2.8) until converged to the steady-state voltage of OCV. The term  $\tau = R_1 \cdot C_1$  in Eq. (2.8) is the time-constant of the  $R_1$  &  $C_1$  parallel network in Fig. 2.2, which describes how quickly the battery voltage stabilizes. Eqs. (2.6)–(2.8) are the basis for BPM to estimate the battery parameters  $\langle OCV, R_0, R_1, C_1 \rangle$  from the battery voltage, as we describe next.

Estimating Battery Parameters Using Voltage. BPM profiles the battery parameters at a set of discretized SoC levels:  $\{0\%, \Delta\%, 2\Delta\%, \cdots, 100\%\}$ . BPM charges the battery with current  $I_c$  until the next SoC level is reached, rests the battery by disabling the charging for  $t_r$ , and then estimates the battery parameters at the current SoC level using the battery voltage during resting, as illustrated in

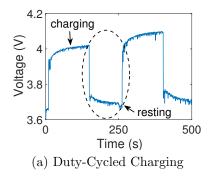

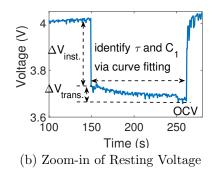

Figure 2.11: Estimating battery parameters using battery voltage during resting.

Fig. 2.11 with  $\Delta = 2$  and a resting period of  $t_l = 100$ s. Specifically, BPM estimates the battery parameters using the resting voltage based on Eqs. (2.6)–(2.8) as follows:

- it estimates  $R_0$  from the instantaneous voltage drop according to  $R_0 = \Delta V_{inst.}/I_c$ ;

- it estimates  $R_1$  based on the transient voltage drop to the steady-state voltage  $R_1 = \Delta V_{trans.}/I_c$ ;

- it estimates  $C_1$  from the time constant  $(\tau = R_1 \cdot C_1)$  of the voltage response via least-square curve-fitting; and

- it estimates the OCV as the steady-state voltage.

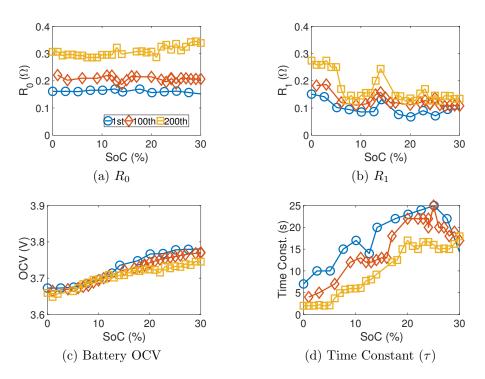

Note that the 100-s rest period in Fig. 2.11 is determined based on Eq. (2.8): the battery voltage converges to OCV at a rate of  $1 - e^{\frac{t}{\tau}}$ . For example, with the maximum  $\tau$  of approximately 25s observed in Fig. 2.12, a 100s rest allows the voltage to converge to OCV  $1 - e^{100s/25s} \approx 98\%$ .

Fig. 2.12 plots the thus-estimated parameters of a battery used by a Nexus 5X, for the SoC range of [0,30]%, at the {1st, 100th, 200th} charging cycles. Unlike  $R_0$  which is relatively stable across a given charging cycle,  $R_1$  and  $\tau$  vary significantly with the SoC because of phase transitions [22], causing different voltage drops at different SoC levels even with the same discharge current. Moreover, these battery parameters change significantly over charging cycles: battery impedances increase

Figure 2.12: Battery parameters estimated at different SoC levels for the 1st, 100th, and 200th charging cycles.

while the time-constant (i.e.,  $\tau$  in Eq. (2.8)) decreases, thereby reducing the battery power capacity over time. This explains why devices with aged batteries are likely to experience more unexpected shutoffs.

Capturing Batteries' Temperature-Dependency. Battery parameters also vary with temperature, which BPM must capture to facilitate the compensation of battery parameters based on the runtime environment temperature. Clearly, empirically capturing battery parameters at all potential temperature is impractical; moreover, overnight device charging usually occurs at room temperature. Thus, asking users are required to assist in profiling the parameters at different temperatures, which requests too much effort from them. To overcome this challenge, BPM estimates the battery parameters at various runtime temperatures based on those at room temperature using an offline constructed temperature-dependency model. Specifically, we profiled

<sup>&</sup>lt;sup>7</sup>Accurate offline temperature-dependency model is known to generate reliable battery parameter estimation over battery aging [116].

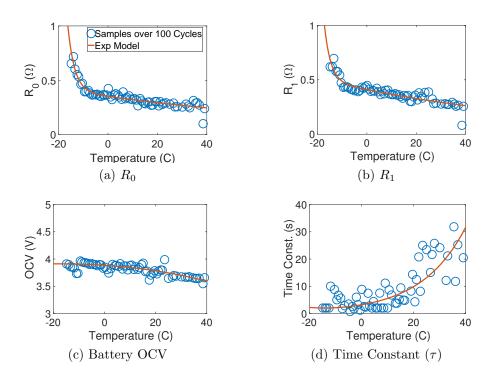

Figure 2.13: Validating the temperature-dependency model over 100 cycles with Nexus 5X battery.

Table 2.1: Summary of the regression model.

| Parameters              | $[a_0, b_0, c_0, d_0]$        | RMSE  | Adj. $\mathbb{R}^2$ |

|-------------------------|-------------------------------|-------|---------------------|

| $R_0(\Omega)$           | [1.2e-4, -5.7, 1.1, -0.14]    | 0.051 | 0.979               |

| $R_1(\Omega)$           | [0.94, -0.17, 2.3e-5, -6.2]   | 0.044 | 0.968               |

| OCV(V)                  | [1.0, -2.4e-2, -3.9e-5, -4.8] | 0.095 | 0.946               |

| Time Constant $\tau(s)$ | [0.15, -0.47, 0.47, 0.37]     | 2.11  | 0.884               |

battery parameters at different temperatures, using a thermal chamber. For example, BPM compensates the temperature's impact on  $R_0$  using

$$R_0(T_b) = (a_0 \cdot e^{b_0 \cdot T_b} + c_0 \cdot e^{d_0 \cdot T_b}) \cdot R_0^r(SoC\%).$$

(2.9)

where  $R_0^r(SoC\%)$  is the  $R_0$  at room temperature for the current SoC level (SoC%) and  $a_0, b_0, c_0, d_0$  are the regression coefficients. We then empirically examined the accuracy of the temperature-dependency model over extended battery discharging cycles. Fig. 2.13 plots the measured battery parameters (circle labels) over 100 cycles at different battery temperatures, justifying the use of a set of exponential regression

Figure 2.14: The processor incurs a burstier discharge current than other components.

models (solid line) to capture the battery's temperature-dependency. Table 2.1 summarizes these regression models and the corresponding model validation errors.

In summary, during the over-night charging process, BPM first estimates the parameters at each SoC, and then, using the temperature-dependency model, it estimates the parameters at different battery temperatures to construct a set of lookup table for battery parameters at different SoC and temperature levels.<sup>8</sup>

## 2.4.3 Regulating Battery Voltage During Discharging

BPM uses the above-constructed battery profile to mitigate unexpected shutoffs of mobile devices and extend their operation, by (i) regulating the discharge current based on real-time battery impedance through adjusting the maximum processor frequency, and (ii) restoring the battery voltage to a safe level by resting the battery before performing the next operation. BPM employs the processor frequency and scheduling as control knobs for regulating the device's discharge current because the processor dominates the dynamics thereof, as we explain below.

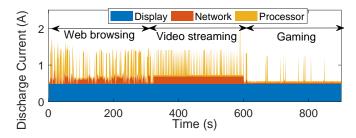

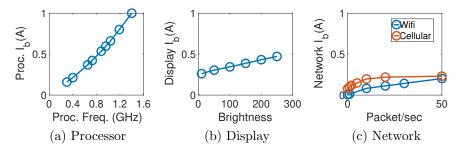

Modeling a Device's Discharge Current. Processor, network and display modules are the dominant energy consumers in a mobile device [124, 126]. Fig. 2.14 plots the discharge current required to run these modules on a Nexus 5X, collected with PowerTutor [126] during web browsing, video streaming, and 3D gaming.

$<sup>^8</sup>$ The lookup table on Nexus 5X contains the battery parameters from -20°C to 40°C battery temperature with a 0.4°C interval equal to the temperature sensor precision, and from 0% to 100% SoC with a 2% interval. The space overhead is only 0.03MB or 0.0015% of total memory.

Figure 2.15: Component-specific discharge currents.

Figure 2.16: Processor frequency variations during the phone's real-life usage.

Whereas the currents drawn by the display and network modules are relatively stable, the processor's current draw varies greatly, implying that the processor dominates the dynamics of the device's discharge current. We further examined the discharge current of each module with different configurations. Specifically, Fig. 2.15 plots the collected processor discharge current at different frequencies (Fig. 2.15a); the display's discharge current at different levels of brightness (Fig. 2.15b); and the network module's discharge current at different packet transmission rates (Fig. 2.15c), showing that the processor discharge current is much more sensitive to its configuration (i.e., frequency) than those of the display and network modules. To further examine whether such dynamic processor frequencies exist in practice, we plotted the processor frequency and discharge current in Fig. 2.16 during the phone's real-life usage, confirming the dynamics of processor frequency and the thus-caused dynamics of discharge current.

Inspired by the above mentioned empirical observations, we abstracted the discharge current of mobile devices with two components: a stable background

current  $I_{bg}$  and dynamic current  $I_{dyn}$ . The background current  $I_{bg}$  is contributed by components other than the processor and the idle processor leakage, and the dynamic current  $I_{dyn}$  is drawn by the active processor performing the computation. Thus, the discharge current during the busy period  $I_b^{busy}$  and the idle period  $I_b^{idle}$  can be captured using

$$I_b^{busy} = I_{dyn} + I_{bg}$$

and  $I_b^{idle} = I_{bg}$ . (2.10)

Furthermore, the dynamic current  $I_{dyn}$  is usually described by the dynamic power model [121, 126]:

$$I_{dyn} = V_p^2 \cdot f_p \cdot \alpha, \tag{2.11}$$

where  $V_p$  and  $f_p$  are the processor voltage and frequency,<sup>9</sup> and  $\alpha$  is a scaling factor that can be empirically identified based on the relationship between discharge current and processor frequency (e.g., as shown in Fig. 2.15a) [90,124]. Through this, we can obtain the average discharge current using the processor utilization  $U_p$ :

$$I_b = I_{dyn}(U_p) + I_{bq}.$$

(2.12)

Controlling Maximum Processor Frequency. BPM regulates the processor frequency to control the dynamic discharge current, without incurring noticeable impact on user experience (e.g., dimming of the screen in battery saver mode). BPM checks the constructed battery profile with the current SoC/temperature every control period to determine the maximum allowed discharge current (i.e., the cutoff current  $I_{cutoff}$ ), and then determines the maximum feasible processor frequency based on  $I_{cutoff}$ .

The cutoff current is determined using Eq. (2.4) to maintain the battery voltage

<sup>&</sup>lt;sup>9</sup>On commodity mobile devices, the processor voltage  $V_p$  is set based on a given frequency  $f_p$  in a pre-defined DVFS table, i.e., there is a one-to-one mapping between voltage and frequency.

above  $V_b^{cutff}$ ; that is,

$$V_b(t) = OCV - (R_0 + R_1)I_b + R_1C_1\frac{dV_b(t)}{dt} \ge V_b^{cutff}.$$

(2.13)

To meet the constraint, in the extreme case of  $\tau \to 0$  (e.g., in the low SoC levels as in Fig. 2.12(d)), we obtain

$$I_b \le \frac{OCV - V_b^{cutff}}{R_0 + R_1} = I_{cutoff}.$$

(2.14)

Note that both  $R_0$  and  $R_1$  depend on battery SoC and temperature, making  $I_{cutoff}$  SoC/temperature-dependent. In every control period, BPM first identifies the dynamic and background current (i.e.,  $I_{dyn}$  and  $I_{bg}$ ):  $I_{dyn}$  is determined based on the current processor frequency using Eq. (2.11), and then, by sampling the processor utilization  $U_p$  and discharge current  $I_b$ , BPM estimates  $I_{bg}$  based on  $\{I_b, I_{dyn}, U_p\}$  using Eq. (2.12). BPM then identifies the maximum processor frequency that regulates the discharge current below  $I_{cutoff}$ , by plugging the thus-obtained  $I_{bg}$  and  $U_p$  into Eq. (2.12). This way, BPM allows the processor to run at the maximum available frequency when the battery voltage is high, and adaptively reduces the maximum processor frequency to the required degree when the battery is low. Additionally, BPM is compatible with existing low-power DVFS schemes because it only limits the maximum processor frequency, within which the processor frequency can still be dynamically adapted to the workload.

Moreover, BPM must determine its control period. Inspired by the fact that the battery voltage changes gradually with the time-constant  $\tau = R_1 \cdot C_1$  in Eq. (2.8), we used the time-constant for the current SoC level as the control period.

Resting the Battery to Restore Voltage. On top of regulating the OS-layer processor frequency, BPM further captures application-level task executions and schedules a rest period between consecutive executions to restore the battery

Figure 2.17: Battery voltage with and without inserting rest periods between task executions.

voltage. Specifically, BPM schedules an idling thread with the highest priority, which is triggered upon the completion of every task to insert a rest period. Fig. 2.17 compares the battery voltage with and without rest periods inserted between task executions. While both cases have the same average discharge current, (i) a continuous workload without resting reduces the battery voltage below the operable level (see Fig. 2.17a), and (ii) by efficiently inserting rest periods (see Fig. 2.17b), the battery voltage is restored during rest periods and thus stays above the operable level.

To efficiently schedule battery resting, we need to determine when and for how long to insert such rest periods. According to Eqs. (2.4) and (2.10), we obtain two voltage levels: (i) when the processor is busy and drawing  $I_b^{busy}$ , the stable-state battery voltage is

$$V_b^{busy} = OCV - (R_0 + R_1) \cdot (I_b^{dyn} + I_b^{idle}), \tag{2.15}$$

and (ii) when the processor is idle, the battery voltage recovers to

$$V_b^{idle} = OCV - (R_0 + R_1) \cdot I_b^{idle}. \tag{2.16}$$

Clearly, no rest time distribution is required if  $V_b^{busy} \geq V_b^{cutoff}$ . Let  $T_{exec}$  be a

Figure 2.18: Control flow of BPM's battery-aware discharging management.

task's execution time.<sup>10</sup> BPM first identifies the safe voltage  $V_{safe}$  that allows the task execution without dropping the voltage below  $V_b^{cutoff}$ , as illustrated in Fig. 2.17,

$$V_b(T_{exec}) = (V_{safe} - V_b^{busy}) \cdot e^{\frac{-T_{exec}}{R_1 \cdot C_1}} + V_b^{busy} = V_b^{cutff}. \tag{2.17}$$

Then, we can find the rest period that can recover the battery voltage to  $V_{safe}$ :

$$V_b(T_{rest}) = \left(V_b^{cutff} - V_b^{idle}\right) \cdot e^{\frac{-T_{rest}}{R_1 \cdot C_1}} + V_b^{idle} = V_b^{safe}. \tag{2.18}$$